Soc Dft Implementation Asdtglobal

Soc Dft Implementation Asdtglobal Our expert team is uniquely positioned to develop a cohesive strategy and implement design for test (dft) solutions that enhances ic testability during the post silicon phase, ensuring a successful first pass silicon outcome. Scan insertion is the most basic and widely used structural dft technique, but dft is not limited to it. socs are complex and io visibility is limited. muxed based signal observation is one of the many ways to view internal signals.

Vlsi Soc Design Two Pillars Of Dft Controllability 40 Off The purpose of this thesis is to study how dft can be utilized to improve testability of a chip and to implement said strategies to a design. the design used for this work is head sail, a heterogenous system on chip with modern features designed as a collaboration of multiple entities. The dft architecture is defined based on the test methodology to achieve test goals which include fast dft sign off, minimized test time, high test coverage and efficient diagnosis. To resolve this issue, in addition to compressed scan, memory bist, and boundary scan dft, we perform high quality testing using various types of dft technology for improved test quality and yield. To successfully meet all the design goals of enormously complex socs, new design and dft technologies must be deployed to enable swift and simultaneous convergence of all constraints: function,.

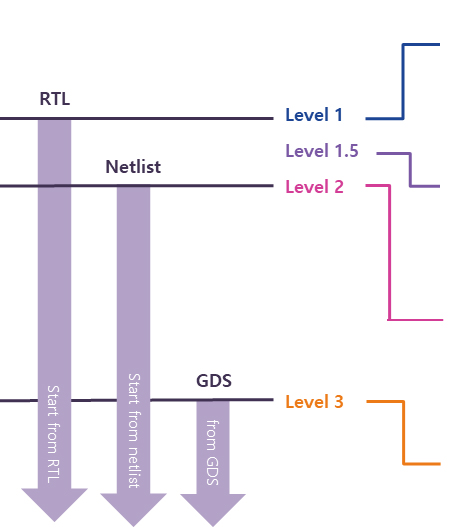

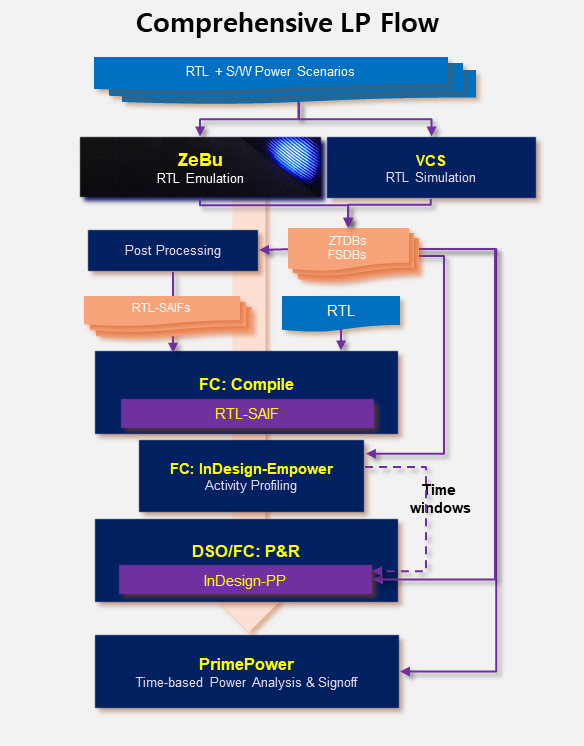

Soc Design Implementation Asdtglobal To resolve this issue, in addition to compressed scan, memory bist, and boundary scan dft, we perform high quality testing using various types of dft technology for improved test quality and yield. To successfully meet all the design goals of enormously complex socs, new design and dft technologies must be deployed to enable swift and simultaneous convergence of all constraints: function,. It explains the methodology widely followed for soc dft and the automatic test pattern generation (atpg) techniques. it covers the major challenges faced during soc design in the context of dft. The basic issue with dft for advanced socs is the size of problem and the need to have a plan to manage dft functions at the soc level. we will show how a smart hierarchical dft methodology dramatically simplifies the problem. In conclusion, verifying the connectivity of soc designs at rtl and netlist for both functional and test modes with complex configurations and dft architectures presents challenges. Advanced system design technologies (asdt) is a leading provider of logical, physical, dft and sign off implementation solutions for system on chip (soc) designs.

Soc Design Implementation Asdtglobal It explains the methodology widely followed for soc dft and the automatic test pattern generation (atpg) techniques. it covers the major challenges faced during soc design in the context of dft. The basic issue with dft for advanced socs is the size of problem and the need to have a plan to manage dft functions at the soc level. we will show how a smart hierarchical dft methodology dramatically simplifies the problem. In conclusion, verifying the connectivity of soc designs at rtl and netlist for both functional and test modes with complex configurations and dft architectures presents challenges. Advanced system design technologies (asdt) is a leading provider of logical, physical, dft and sign off implementation solutions for system on chip (soc) designs.

Soc Design Implementation Asdtglobal In conclusion, verifying the connectivity of soc designs at rtl and netlist for both functional and test modes with complex configurations and dft architectures presents challenges. Advanced system design technologies (asdt) is a leading provider of logical, physical, dft and sign off implementation solutions for system on chip (soc) designs.

Dft

Comments are closed.