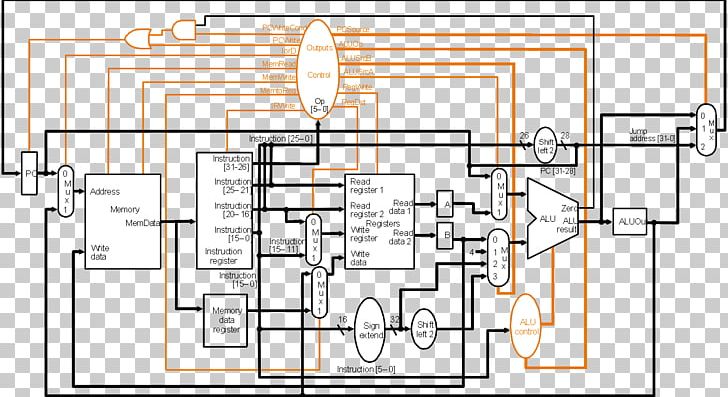

Single Cycle Processor Pdf Central Processing Unit Microprocessor

Mips Architecture Datapath Central Processing Unit Microprocessor Because they use less hardware than single cycle processors, multicycle intel processors have been processors were the historical choice for inexpensive systems. Single cycle processor intro last updated 7 18 23 processor architecture • harvard – separate instruction and data memory paths.

Microprocessor Download Free Pdf Central Processing Unit Building a simple computer we will now look the design of a single cycle processor, i.e., it executes its instructions in a single clock cycle we gradually develop the datapath by adding new components to the state elements. in doing so, we gradually increase the capability of the computer. Starting today: single cycle processor: advantage: one clock cycle per instruction disadvantage: long cycle time et = insts * cpi * cyc time execute an entire instruction we're ready to look at an implementation of the mips simplified to contain only: memory reference instructions: lw, sw arithmetic logical instructions: add, sub, and, or, slt. Single cycle datapath and control design: advantage: one clock cycle per instruction. The design of a single cycle risc v processor represents a significant leap in microprocessor architecture. its minimalist design, open source risc v instruction set, and single cycle execution offer efficiency, scalability, and adaptability, making it an ideal choice for modern computing systems.

Microprocessor Chap2 Pdf Central Processing Unit Microprocessor Single cycle datapath and control design: advantage: one clock cycle per instruction. The design of a single cycle risc v processor represents a significant leap in microprocessor architecture. its minimalist design, open source risc v instruction set, and single cycle execution offer efficiency, scalability, and adaptability, making it an ideal choice for modern computing systems. This chapter contents the basic units in the cpu functions of the major components in the cpu instruction execution at hardware level performance and trace off among cpus. Single cycle design – fetch, decode, and execute each instruction in one (and only one) clock cycle. no datapath resource can be used more than once per instruction, so some must be duplicated (e.g., separate instruction memory and data memory, several adders). The cpu is sometimes called the processor, or in the personal computer field called “microprocessor”. it is a single integrated circuit that contains all the electronics needed to execute a program. Catherine has bought a new laptop computer which was advertised as having a 1.6ghz dual core central processing unit (cpu) and 512kb level 1 cache. state the purpose of the cpu.

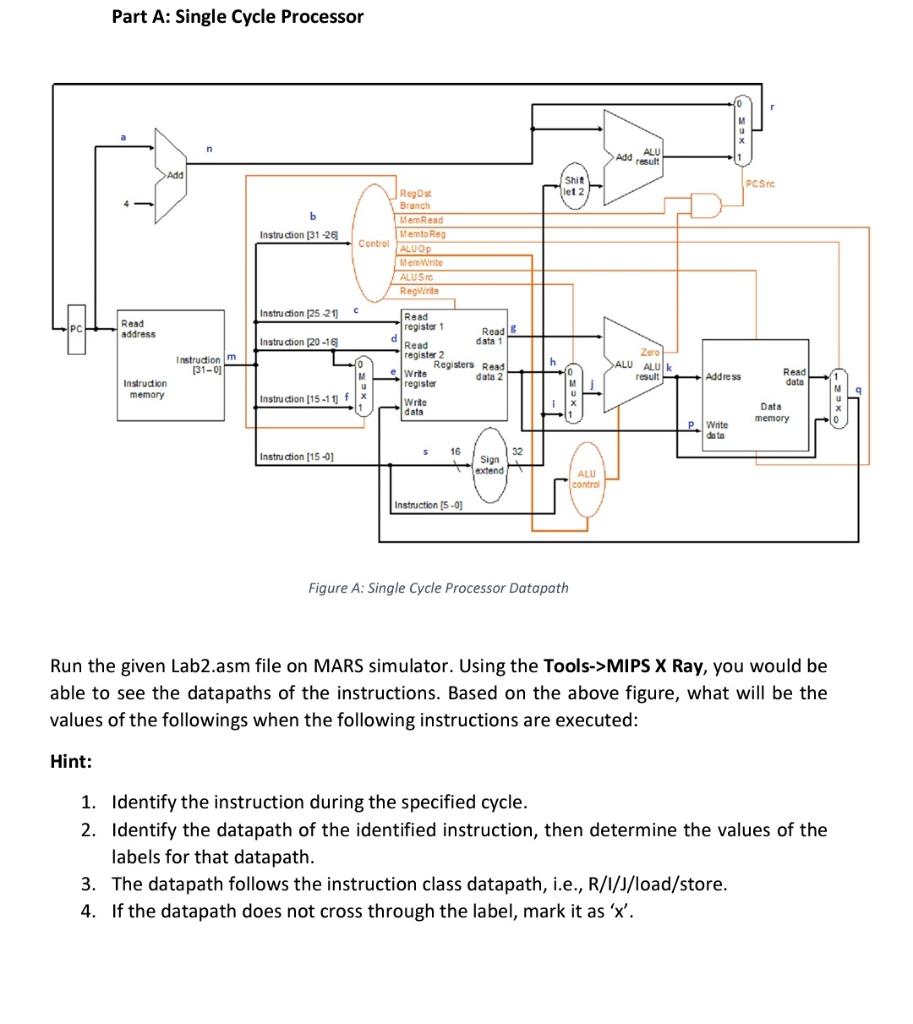

Single Cycle Processor Lab Cpu20241 Pdf At Main V Kr0pt Single Cycle This chapter contents the basic units in the cpu functions of the major components in the cpu instruction execution at hardware level performance and trace off among cpus. Single cycle design – fetch, decode, and execute each instruction in one (and only one) clock cycle. no datapath resource can be used more than once per instruction, so some must be duplicated (e.g., separate instruction memory and data memory, several adders). The cpu is sometimes called the processor, or in the personal computer field called “microprocessor”. it is a single integrated circuit that contains all the electronics needed to execute a program. Catherine has bought a new laptop computer which was advertised as having a 1.6ghz dual core central processing unit (cpu) and 512kb level 1 cache. state the purpose of the cpu.

Part A Single Cycle Processor Figure A Single Cycle Chegg The cpu is sometimes called the processor, or in the personal computer field called “microprocessor”. it is a single integrated circuit that contains all the electronics needed to execute a program. Catherine has bought a new laptop computer which was advertised as having a 1.6ghz dual core central processing unit (cpu) and 512kb level 1 cache. state the purpose of the cpu.

Comments are closed.