Schematic Diagram Of The 6t Sram Cell Download Scientific Diagram

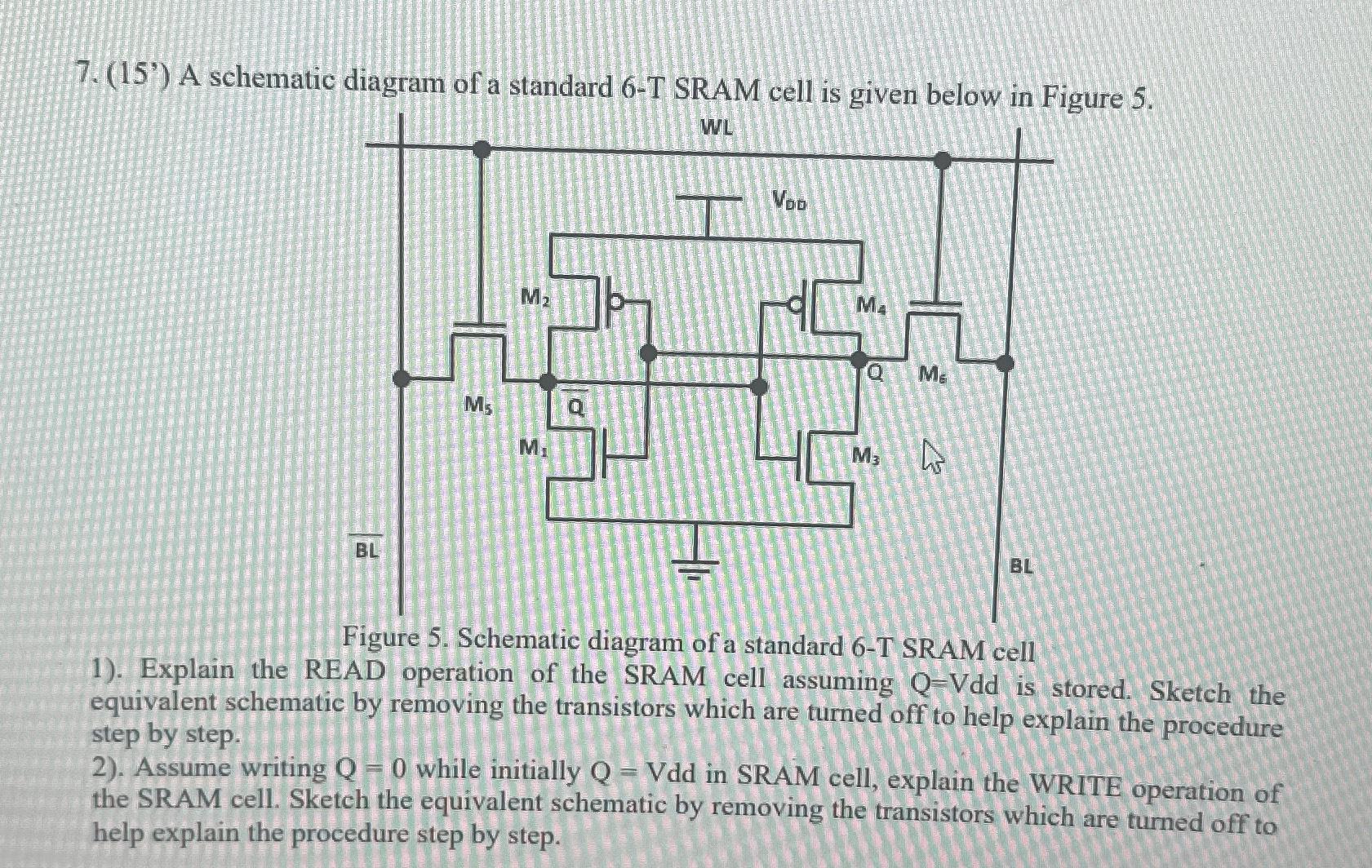

15 ï A Schematic Diagram Of A Standard 6 T Sram Chegg Download scientific diagram | schematic diagram of 6t sram cell from publication: design of novel sram cell using hybrid vlsi techniques for low leakage and high speed in. This image shows the complete schematic of the 6 transistor sram cell designed in cadence virtuoso schematic editor. the design implements a standard cmos 6t sram cell with cross coupled inverters for data storage.

Schematic Diagram Of 10t Sram Cell Download Scientific Diagram The document discusses the 6 transistor static random access memory (sram) cell. the sram cell consists of two cross coupled cmos inverters to store a bit of information and two access transistors to read from and write to the cell. Abstract vlsi chips due to its unique capability to retain data. this memory cell has become a subject of resear h to meet the demands for future communication systems. in this paper a 6t s am cell is designed by using verilog and esim software. static random access memory (sram) is a static memory. In this paper we present a new static random access memory (sram) that has 7 transistors in each cell. this idea allows for bit interleaving that makes the sram more reliable against the soft. This project report details the architecture of serial peripheral interface (spi) for a 32 byte static random access memory (sram) which was designed, simulated and tested using an 0.6um cmos.

Schematic Diagram Of 6t Sram Cell Download Scientific Diagram In this paper we present a new static random access memory (sram) that has 7 transistors in each cell. this idea allows for bit interleaving that makes the sram more reliable against the soft. This project report details the architecture of serial peripheral interface (spi) for a 32 byte static random access memory (sram) which was designed, simulated and tested using an 0.6um cmos. The conventional 6t sram memory cell is composed of two cross coupled cmos inverters with two pass transistors connected to complementary bit lines. The schematic diagram of conventional 6t sram cell. in this paper, we design different type of sram cells. this paper compares the performance of five sram cell topologies, which. We, in our work, have designed and compared sram cells under different configurations (6t, 8t & 9t) on the basis of read and write delay, leakage power consumption and stability i.e., noise. 6t sram cell and layouts a, schematic of 6t sram cell includes two pull up (p1 and p2), two pull down (n1 and n2) and two pass gate (a1 and a2) transistors. blb and bl are the bit.

Comments are closed.