Ppt Exploring Basic Sequential Circuits In Verilog Latches Flip

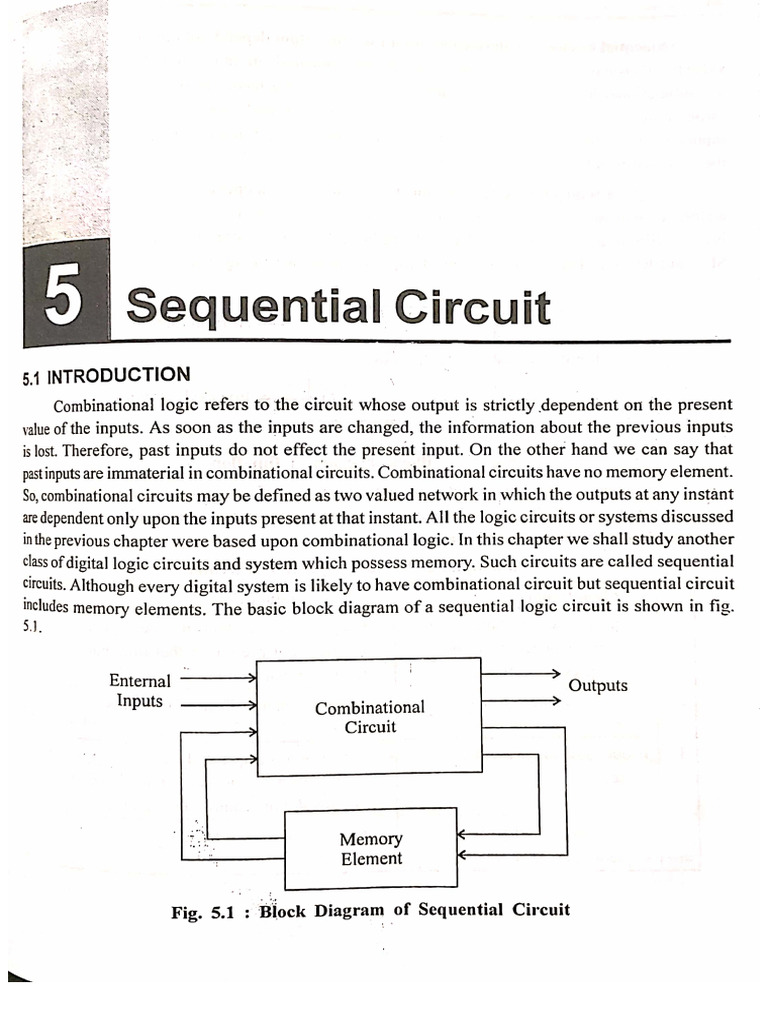

Lecture 9 Updated Sequential Circuits Latches Flip Flops Download This lecture delves into the fundamental concepts of basic sequential circuits using verilog, covering latches, flip flops, registers, counters, shift registers, datapaths, and state machines. This document provides an overview of sequential circuits such as latches and flip flops. it defines sequential circuits and explains that they produce outputs based on current and previous inputs.

Unit Iv Sequential Circuit Latches Flip Flops Analysis Of Clocked But a flop is made of two latches! 11: sequential circuits * min delay: pulsed latches hold time increased by pulse width 11: sequential circuits * time borrowing in a flop based system: data launches on one rising edge must setup before next rising edge if it arrives late, system fails if it arrives early, time is wasted flops have hard edges. Lecture 5: sequential circuit design circuits using flip flops now that we know inputs outputs combinational circuit about flip flops and what they do, how do we use them in circuit storage units design?. Flip flops are memory elements that change state on clock signals. Latches and flip flops differ in the method used for changing their state. memory element: a device which can remember value indefinitely, or change value on command from its inputs. memory element with clock. flip flops are memory elements that change state on clock signals. clock is usually a square wave. complementary outputs: q and q'.

Sequential Circuits Latches And Flip Flops Pdf Telecommunications Flip flops are memory elements that change state on clock signals. Latches and flip flops differ in the method used for changing their state. memory element: a device which can remember value indefinitely, or change value on command from its inputs. memory element with clock. flip flops are memory elements that change state on clock signals. clock is usually a square wave. complementary outputs: q and q'. Modeling latches and flip flops. blocking versus non blocking assignments. modeling sequential circuit diagrams. modeling mealy and moore state diagrams. writing test benches for sequential circuits. modeling registers and counters. recall: sensitivity list of always block. syntax: always @(sensitivity list) begin. procedural statements. end. Specifically, it covers rs latches, d latches, edge triggered flip flops using master slave configuration and sr latches. it also discusses shift registers, synchronous counters, and describes sequential circuits using verilog. But a sequential circuit “remembers” its previous state. its output depends on present inputs and previous state. Unit 11 latches and flip flops fundamentals of logic design by roth and kinney 11.1 introduction sequential circuits have the property that the output depends not – id: 7886a7 ndy0y.

Ppt Sequential Circuits Latches Flip Flops Powerpoint Presentation Modeling latches and flip flops. blocking versus non blocking assignments. modeling sequential circuit diagrams. modeling mealy and moore state diagrams. writing test benches for sequential circuits. modeling registers and counters. recall: sensitivity list of always block. syntax: always @(sensitivity list) begin. procedural statements. end. Specifically, it covers rs latches, d latches, edge triggered flip flops using master slave configuration and sr latches. it also discusses shift registers, synchronous counters, and describes sequential circuits using verilog. But a sequential circuit “remembers” its previous state. its output depends on present inputs and previous state. Unit 11 latches and flip flops fundamentals of logic design by roth and kinney 11.1 introduction sequential circuits have the property that the output depends not – id: 7886a7 ndy0y.

Modelling Flip Flops And Latches In Verilog But a sequential circuit “remembers” its previous state. its output depends on present inputs and previous state. Unit 11 latches and flip flops fundamentals of logic design by roth and kinney 11.1 introduction sequential circuits have the property that the output depends not – id: 7886a7 ndy0y.

Comments are closed.