Pdf Efficient Vlsi Architecture For Variable Length Block Lms

Pdf Efficient Vlsi Architecture For Variable Length Block Lms Using the proposed scheme, we have derived an efficient architecture for blms fir filter. the proposed structure can be reconfigured for different filter lengths with negligible overhead. Therefore, the proposed architecture is suitable for efficient fpga realization of an lms fir adaptive filter for real time digital signal processing applications.

Vlsi Architectures And Implementations Pdf Low Density Parity Check Using the proposed scheme, they have derived an efficient architecture for blms fir filter. the proposed structure can be reconfigured for different filter lengths with negligible overhead complexity and it supports variable convergence factor. Using the proposed scheme, they have derived an efficient architecture for blms fir filter. the proposed structure can be reconfigured for different filter lengths with negligible overhead complexity and it supports variable convergence factor. Using the proposed scheme, we have derived an efficient architecture for blms fir filter. the proposed structure can be reconfigured for different filter lengths with negligible overhead complexity and it supports variable convergence factor μ. Abstract this thesis presents a new area and power efficient vlsi architecture for least mean square (lms) adaptive filter using distributed arithmetic (da). conventionally, da based lms adaptive filter requires look up tables (luts) for filtering and weight updating operations.

Figure 2 From A Vlsi Architecture For H 264 Avc Variable Block Size Using the proposed scheme, we have derived an efficient architecture for blms fir filter. the proposed structure can be reconfigured for different filter lengths with negligible overhead complexity and it supports variable convergence factor μ. Abstract this thesis presents a new area and power efficient vlsi architecture for least mean square (lms) adaptive filter using distributed arithmetic (da). conventionally, da based lms adaptive filter requires look up tables (luts) for filtering and weight updating operations. New straightforward versions of the weight update block, offset term, and shift accumulate unit are proposed. optimal tuning of the least mean square (lms) algorithm enables a trade off between speed and power consumption. The simulation and implementation of very large scale integration (vlsi) architecture are done using matlab, vivado suite and complementary metal–oxide– semiconductor (cmos) 90 nm technology node using cadence rtl and genus compiler respectively. Using the proposed scheme, we have derived an efficient architecture for blms fir filter. the proposed structure can be reconfigured for different filter lengths with negligible overhead complexity and it supports variable convergence factor µ. Sub filters, where m = n=l, n is the filter length and l is the bl ck size. each sub filter acts like a short length blms fir filter of size l. the proposed decomposition scheme favors time.

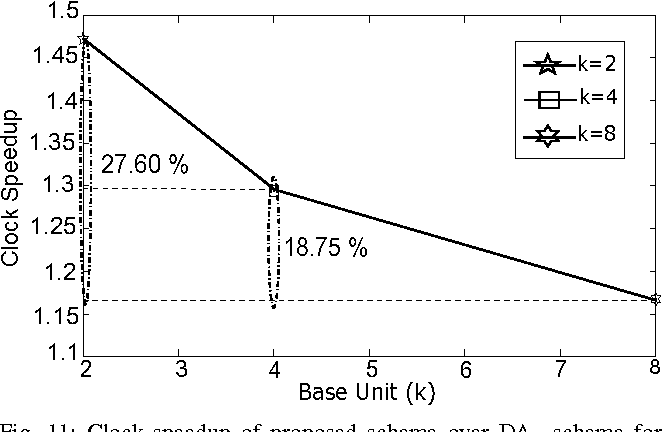

Figure 11 From Low Complexity And Critical Path Based Vlsi Architecture New straightforward versions of the weight update block, offset term, and shift accumulate unit are proposed. optimal tuning of the least mean square (lms) algorithm enables a trade off between speed and power consumption. The simulation and implementation of very large scale integration (vlsi) architecture are done using matlab, vivado suite and complementary metal–oxide– semiconductor (cmos) 90 nm technology node using cadence rtl and genus compiler respectively. Using the proposed scheme, we have derived an efficient architecture for blms fir filter. the proposed structure can be reconfigured for different filter lengths with negligible overhead complexity and it supports variable convergence factor µ. Sub filters, where m = n=l, n is the filter length and l is the bl ck size. each sub filter acts like a short length blms fir filter of size l. the proposed decomposition scheme favors time.

Vlsi Vlsi System Vlsi System Design Pdf Field Programmable Gate Using the proposed scheme, we have derived an efficient architecture for blms fir filter. the proposed structure can be reconfigured for different filter lengths with negligible overhead complexity and it supports variable convergence factor µ. Sub filters, where m = n=l, n is the filter length and l is the bl ck size. each sub filter acts like a short length blms fir filter of size l. the proposed decomposition scheme favors time.

Pdf Power Optimized Vlsi Architecture Of Distributed Arithmetic Based

Comments are closed.