Pdf Design Of N To 2n Quantum Reversible Decoder Using Modified

Pdf Design Of N To 2n Quantum Reversible Decoder Using Modified In this paper we tried to design n to 2 ⁿ reversible decoder using modified toffoli reversible logic gates. In this paper we tried to design n to 2n reversible decoder using modified toffoli reversible logic gates. we proposed 1 to 21, 2 to 22 and 3 to 23, 4 to 24 and 5 to 25 reversible decoder and analyzed its lead in respect of quantum cost and garbage output.

Design Of A Ternary Reversible Quantum Adder Using Genetic Algorithm Reversible logic may be a new research area due to its reduction in power dissipation and lots of researchers proposed differing types of approaches to construct a quantum reversible decoder. in this paper we tried to design n to 2 n reversible decoder using modified toffoli reversible logic gates. Abstract the design of low consumption cmos circuits, nanotechnologies and quantum computing has becomed more attached to the reversible logic. a set of gates have been recently exploited in reversible computer science for the design of certain circuits. among them, we find the decoders. In the 3rd section, we exploit a design of each decoder 2 to 4, 3 to 8, and n to 2n from a recent article [13] we modify and show their associated performance criteria. In this work, our goal is to optimize the designs of reversible decoder circuits in terms of all three important parameters, the quantum cost, quantum delay and garbage outputs.

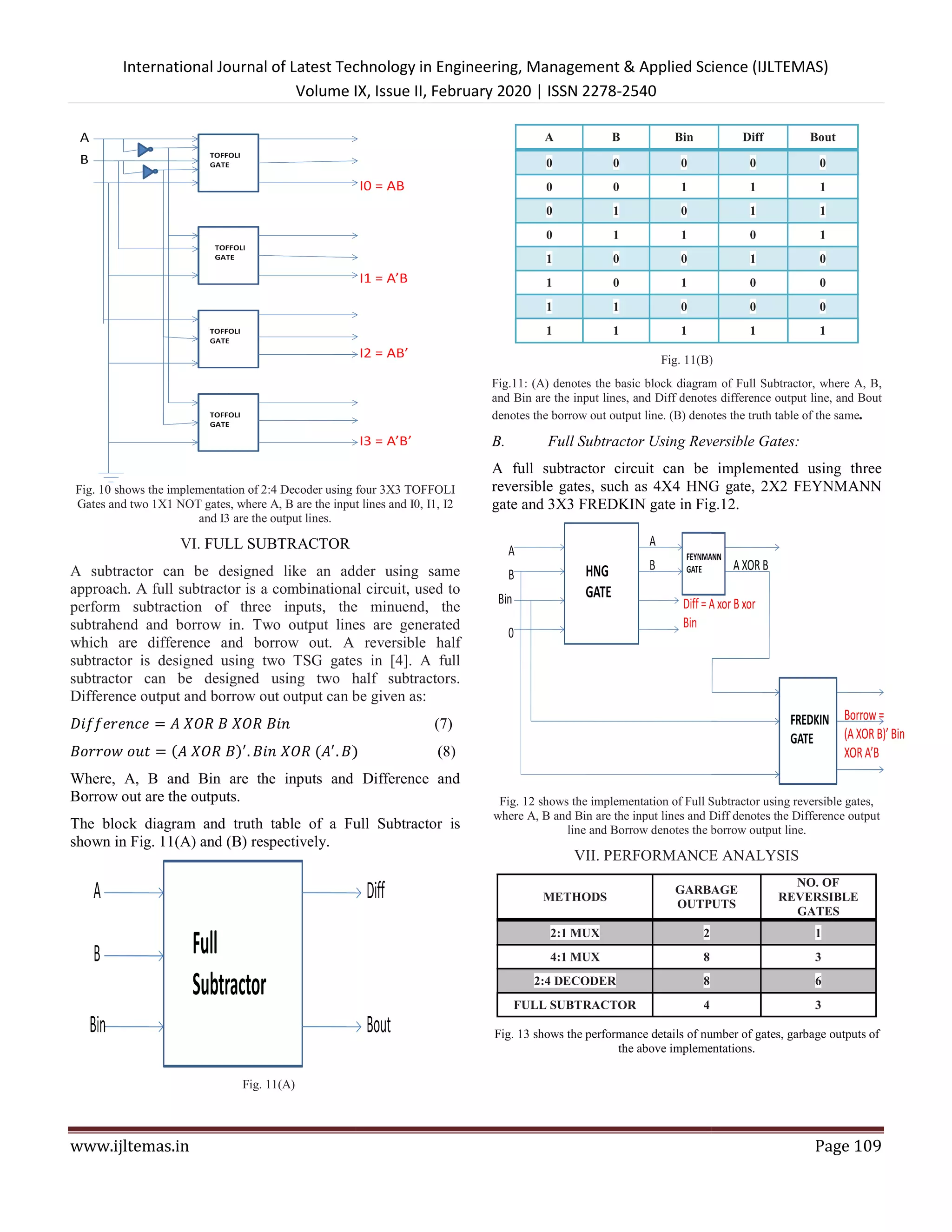

Design Of Multiplexers Decoder And A Full Subtractor Using Reversible In the 3rd section, we exploit a design of each decoder 2 to 4, 3 to 8, and n to 2n from a recent article [13] we modify and show their associated performance criteria. In this work, our goal is to optimize the designs of reversible decoder circuits in terms of all three important parameters, the quantum cost, quantum delay and garbage outputs. Abstract— this paper demonstrates the reversible logic synthesis for the n to 2n decoder, where n is the number of data bits.the circuits are designed using only reversible fault tolerant fredkin and feynman double gates. A compact realization of quantum n to 2n decoder circuit, where n is the number of input bits, which performs better than the existing ones, and is simulated using cadence tool in both analog and digital. This paper presents a compact realization of quantum n to 2n decoder circuit, where n is the number of input bits. the proposed design of the quantum n to 2n decoder circuit shows that it is composed of the quantum 2 to 4 decoder circuit. The low quantum cost and quantum delay means fast computation in the quantum logic circuits. in this article, we have synthesized 2 − to − 4 decoder on three approaches based on s1g, s2g and s3g gates.

A New Nano Design Of Configurable Logic Module Based On Coplanar Abstract— this paper demonstrates the reversible logic synthesis for the n to 2n decoder, where n is the number of data bits.the circuits are designed using only reversible fault tolerant fredkin and feynman double gates. A compact realization of quantum n to 2n decoder circuit, where n is the number of input bits, which performs better than the existing ones, and is simulated using cadence tool in both analog and digital. This paper presents a compact realization of quantum n to 2n decoder circuit, where n is the number of input bits. the proposed design of the quantum n to 2n decoder circuit shows that it is composed of the quantum 2 to 4 decoder circuit. The low quantum cost and quantum delay means fast computation in the quantum logic circuits. in this article, we have synthesized 2 − to − 4 decoder on three approaches based on s1g, s2g and s3g gates.

Pdf Design Of Novel Quantum Reversible Ternary Adder Circuits This paper presents a compact realization of quantum n to 2n decoder circuit, where n is the number of input bits. the proposed design of the quantum n to 2n decoder circuit shows that it is composed of the quantum 2 to 4 decoder circuit. The low quantum cost and quantum delay means fast computation in the quantum logic circuits. in this article, we have synthesized 2 − to − 4 decoder on three approaches based on s1g, s2g and s3g gates.

Comments are closed.