Parity Generator And Parity Checker Explained

Even Parity Generator And Parity Checker Pdf Bit Telecommunications In this article, we will explain the concept of parity checking, the types of parity generators and checkers, their logic circuits and diagrams, and their applications. In implementing generator or checker circuits, unused parity bits must be tied to logic zero and the cascading inputs must not be equal. if this ic is used as an even parity checker and when a parity error occurs, the ‘sum even’ output goes low and ‘sum odd’ output goes high.

Parity Generator And Checker Pdf Electronics Computing A parity generator is a combinational logic circuit used to generate and add a parity to the input or transmitted data, while a parity checker is also a combinational circuit used to verify the correctness of received data. A parity generator is a combinational logic circuit that generates the parity bit in the transmitter. on the other hand, a circuit that checks the parity in the receiver is called parity checker. Parity checkers and generators detect errors in binary data streams. parity checking devices combine a generator and checker into an integrated circuit (ic) package. In this article, how the parity generator and checker generate and check the bit and its types, logic circuits, truth tables, and k map expressions are discussed briefly.

Chapter 7 Parity Bit Generator Checker Pdf Parity checkers and generators detect errors in binary data streams. parity checking devices combine a generator and checker into an integrated circuit (ic) package. In this article, how the parity generator and checker generate and check the bit and its types, logic circuits, truth tables, and k map expressions are discussed briefly. We need to add the parity bit to a signal. this is done by the parity generator. this parity inclusive binary message then transmits from transmitter to receiver end. the parity checker matches the number of 1’s at the receiver’s end with that of the transmitter’s end to check for errors. The document explains the concepts of parity bits, parity generators, and parity checkers used in digital communication to detect errors during data transmission. A parity generator is a combinational logic circuit that generates the parity bit in the transmitter. on the other hand, a circuit that checks the parity in the receiver is called parity. Learn about parity generators and checkers in logic ics. understand their role in error detection, data transmission, and their applications.

17 Parity Generator And Checker 08 02 2023 Pdf Pdf Digital We need to add the parity bit to a signal. this is done by the parity generator. this parity inclusive binary message then transmits from transmitter to receiver end. the parity checker matches the number of 1’s at the receiver’s end with that of the transmitter’s end to check for errors. The document explains the concepts of parity bits, parity generators, and parity checkers used in digital communication to detect errors during data transmission. A parity generator is a combinational logic circuit that generates the parity bit in the transmitter. on the other hand, a circuit that checks the parity in the receiver is called parity. Learn about parity generators and checkers in logic ics. understand their role in error detection, data transmission, and their applications.

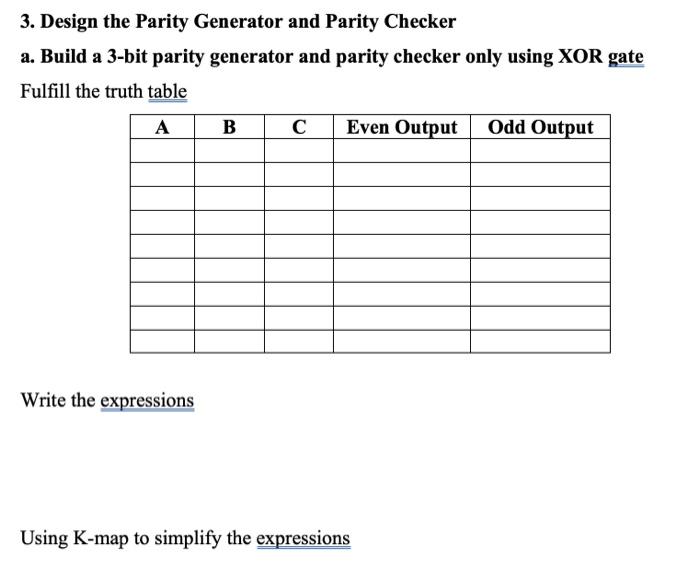

Solved 3 Design The Parity Generator And Parity Checker A Chegg A parity generator is a combinational logic circuit that generates the parity bit in the transmitter. on the other hand, a circuit that checks the parity in the receiver is called parity. Learn about parity generators and checkers in logic ics. understand their role in error detection, data transmission, and their applications.

Comments are closed.