Parity Generator 4 Bit Even Parity

4 Bit Even Parity Checker Pdf Consider a 4 bit digital code 00110 (having 0 as parity bit at lsb position), this code is received by the even parity checker. the parity checker will count the number of 1s in the code which is even (two). Its primary function is to calculate and add the parity bit to the data stream based on the chosen parity scheme (even or odd). the circuit takes the original data stream (e.g., a byte) as input. it performs operations on the data bits based on the chosen scheme (even or odd parity).

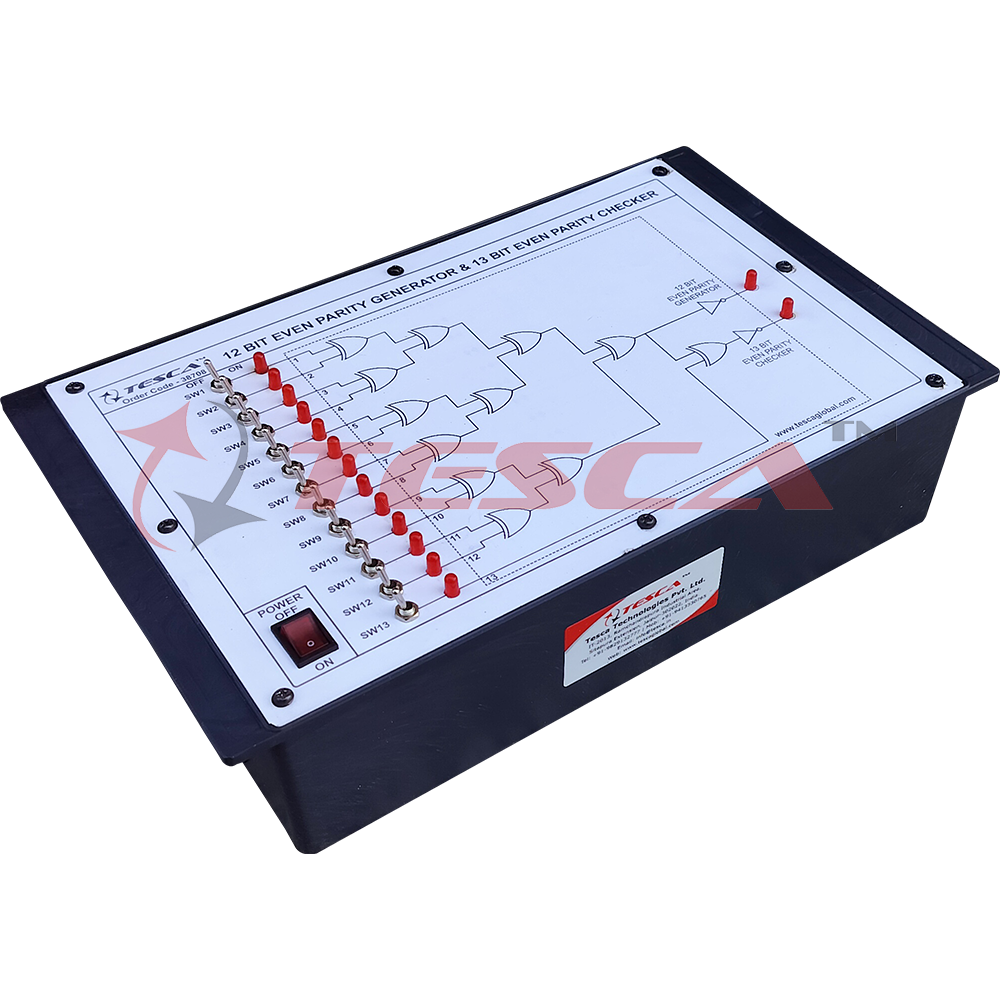

Order Code 38708 The document outlines a lab manual for a digital system design course, focusing on the design of a 4 bit parity generator and checker circuit. it details the apparatus required, the theory behind parity generation for even and odd parities, and includes logic diagrams and truth tables. The parity bit is added to the message bits on the sender side to help in error detection at the receiver side. the binary message ensures an odd or even total of 1’s. Parity generator: generates an even parity bit for a 4 bit input data. parity checker: checks the received data along with the parity bit to detect single bit errors. Definition: computes the parity bit for the given binary input (even or odd) and returns the augmented string or the parity bit.

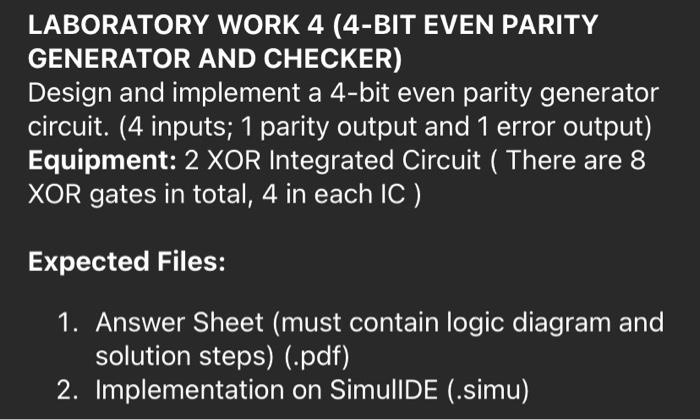

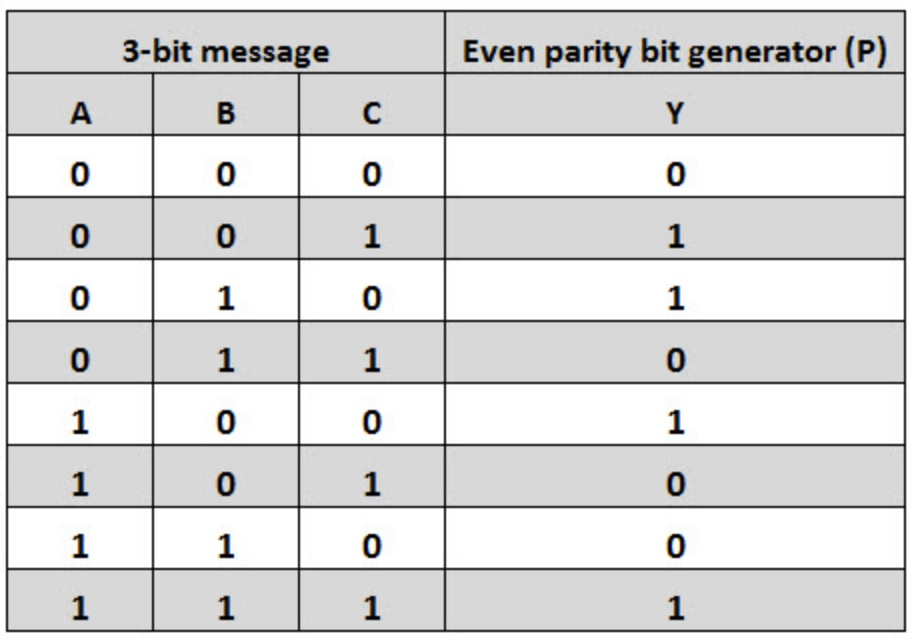

Laboratory Work 4 4 Bit Even Parity Generator And Chegg Parity generator: generates an even parity bit for a 4 bit input data. parity checker: checks the received data along with the parity bit to detect single bit errors. Definition: computes the parity bit for the given binary input (even or odd) and returns the augmented string or the parity bit. To generate the even parity bit for a 4 bit data, three ex or gates are required to add the 4 bits and their sum will be the parity bit. let us consider that the 3 bit data is to be transmitted with an odd parity bit. the three inputs are a, b and c and p is the output parity bit. An even parity generator ensures an even number of 1s in the data word plus the parity bit. if the data word has an odd number of 1s, it adds a 1; if it has an even number of 1s, it adds a 0. Explore digital circuits online with circuitverse. with our easy to use simulator interface, you will be building circuits in no time. To start the applet, please enable java and reload this page. (you might have to restart the browser.) a simple 4 bit parity generator for even parity, built with four xor gates. (note: the corresponding exercise in our introductory courses does not include the hint to use the xor gates.

Solved Consider The Parity Generator Even Parity Shown In Chegg To generate the even parity bit for a 4 bit data, three ex or gates are required to add the 4 bits and their sum will be the parity bit. let us consider that the 3 bit data is to be transmitted with an odd parity bit. the three inputs are a, b and c and p is the output parity bit. An even parity generator ensures an even number of 1s in the data word plus the parity bit. if the data word has an odd number of 1s, it adds a 1; if it has an even number of 1s, it adds a 0. Explore digital circuits online with circuitverse. with our easy to use simulator interface, you will be building circuits in no time. To start the applet, please enable java and reload this page. (you might have to restart the browser.) a simple 4 bit parity generator for even parity, built with four xor gates. (note: the corresponding exercise in our introductory courses does not include the hint to use the xor gates.

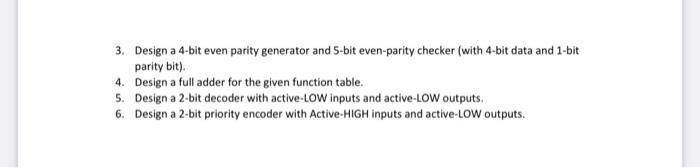

Solved 3 Design A 4 Bit Even Parity Generator And 5 Bit Chegg Explore digital circuits online with circuitverse. with our easy to use simulator interface, you will be building circuits in no time. To start the applet, please enable java and reload this page. (you might have to restart the browser.) a simple 4 bit parity generator for even parity, built with four xor gates. (note: the corresponding exercise in our introductory courses does not include the hint to use the xor gates.

Comments are closed.