Module 2 Sequential Circuits Pdf Logic Gate Electrical Circuits

Sequential Logic Circuits Pdf Logic Gate Electrical Engineering Module 2 sequential circuits free download as pdf file (.pdf), text file (.txt) or read online for free. For a sequential circuit to work properly, we must guarantee that the setup time and hold time constraints of every register will always be satisfied. the setup time constraint is affected by both the logic in the circuit and the clock period. to fix violations, either: the hold time constraint is affected only by the logic in the circuit.

Examples Of Sequential Logic Circuits Introduction to sequential circuits a sequential circuit consists of: 1. memory elements: inputs. However, virtually all sequential circuits currently employ the notion of synchronous operation, that is, the output of a sequential circuit is constrained to change only at a time specified by a global enabling signal. Module 2.2 showed the relationship between a truth table that describes the operation of a circuit, and a boolean equation that describes the logic of the circuit. Let’s learn how to design sequential circuits! we next look at timing constraints for combinational and sequential logic. what about the clock? does the clock edge arrive at the same time to all the d ffs on the chip? the wire has its own delay!!! thold = 70 ps! no!!! max frequency = 1 215 ps = 4.65 ghz!.

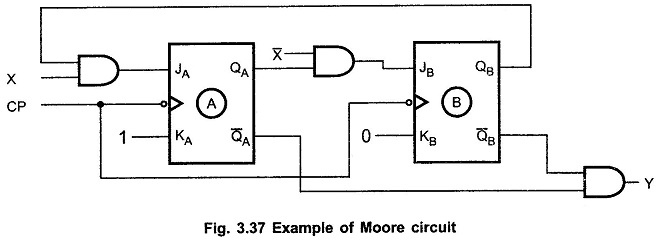

Block Diagram Of Sequential Logic Circuits Wiring Flash Module 2.2 showed the relationship between a truth table that describes the operation of a circuit, and a boolean equation that describes the logic of the circuit. Let’s learn how to design sequential circuits! we next look at timing constraints for combinational and sequential logic. what about the clock? does the clock edge arrive at the same time to all the d ffs on the chip? the wire has its own delay!!! thold = 70 ps! no!!! max frequency = 1 215 ps = 4.65 ghz!. • a clock (b) logic diagram. is a periodic signal that is used to keep time in sequential circuits. Design of synchronous sequential circuits the design of a clocked sequential circuit starts from a set of specifications and ends with a logic diagram (analysis reversed!). High level input voltage and current: the minimum input voltage recognised as logic 1(high level) by the logic gates (2v – 3v range) and the corresponding current is high level input current. Simple, and powerful: logic gates can realize any boolean function, and can be combined to form powerful chips, like an alu but, as a general model of computation, logic gates fall short.

Comments are closed.