Model A Counter For Hdl And High Level Synthesis Code Generation

Model A Counter For Hdl And High Level Synthesis Code Generation To write matlab code that models hardware and is suitable for hdl and high level synthesis (hls) code generation, use this design pattern. Model a counter for hdl and high level synthesis code generation to write matlab code that models hardware and is suitable for hdl and high level synthesis (hls) code generation, use this design pattern.

Hdl Code Generation Onboarding Pdf Hardware Description Language Use simulink model templates for hdl code generation to create efficient hardware designs. This example shows how you can generate hdl code for a simple counter model and synthesize the generated code on a xilinx ® fpga by using the simulink ® hdl workflow advisor. To enhance the performance of large language models (llms) in hardware description language (hdl) code generation without the need for extensive training, it is crucial to leverage the in context learning and reasoning abilities of these models. This example shows how to generate an hdl test bench and verify the generated code for a simple counter model. to generate hdl code for this model, see generate hdl code from simulink model.

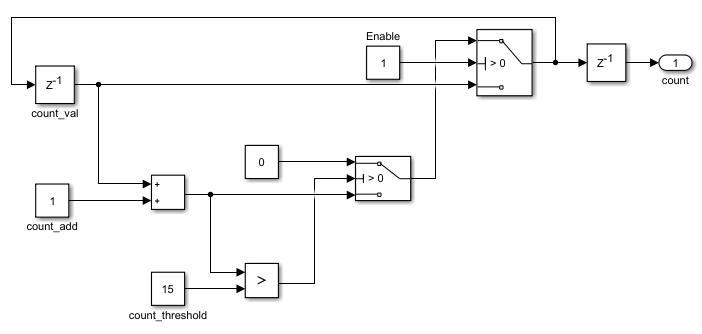

Ppt Hdl Code Generation Using Matlab Simulink Powerpoint Presentation To enhance the performance of large language models (llms) in hardware description language (hdl) code generation without the need for extensive training, it is crucial to leverage the in context learning and reasoning abilities of these models. This example shows how to generate an hdl test bench and verify the generated code for a simple counter model. to generate hdl code for this model, see generate hdl code from simulink model. To create a matlab ® algorithm compatible for hdl code generation, see guidelines for writing matlab code to generate efficient hdl and hls code. the model is a simple counter algorithm that counts upward and wraps back to zero after it reaches the upper limit that you specify. In this article, the design and implementation of a 4 bit up down synchronous counter using verilog hdl was covered. it also gave information about the counters, description of the verilog code and pros and cons of adopting verilog hdl for counters. This research proposes a modern approach based on multi level compiler technologies to bridge the gap between hls and high level frameworks, and to use domain specific abstractions to solve domain specific problems. Use the matlab and hdl coder to design and create testbenches, then use the code generation feature in hdl coder to input into vitis hls for simulation and synthesis on amd adaptive socs and fpgas.

Comments are closed.