Lecture 6 Logic Gate Basics Pdf Logic Gate Cmos

1 4 Lecture Logic Gate And Simple Logic Circuit 20222023 Pdf Lecture 6 logic gate basics free download as pdf file (.pdf), text file (.txt) or view presentation slides online. this document covers the basics of logic gates in cmos vlsi design, focusing on boolean algebra and logic with cmos technology. Welcome to the cs504 logical gate repository! this repository is dedicated to exploring the fundamentals of **logical gates** and their applications in digital circuits and computer systems. whether you're a student, educator, this repository provides a collection of resources, code examples, and projects to help you with logical gates. cs 504 lectures lecture 6 cs504 lecture 6.pdf at main.

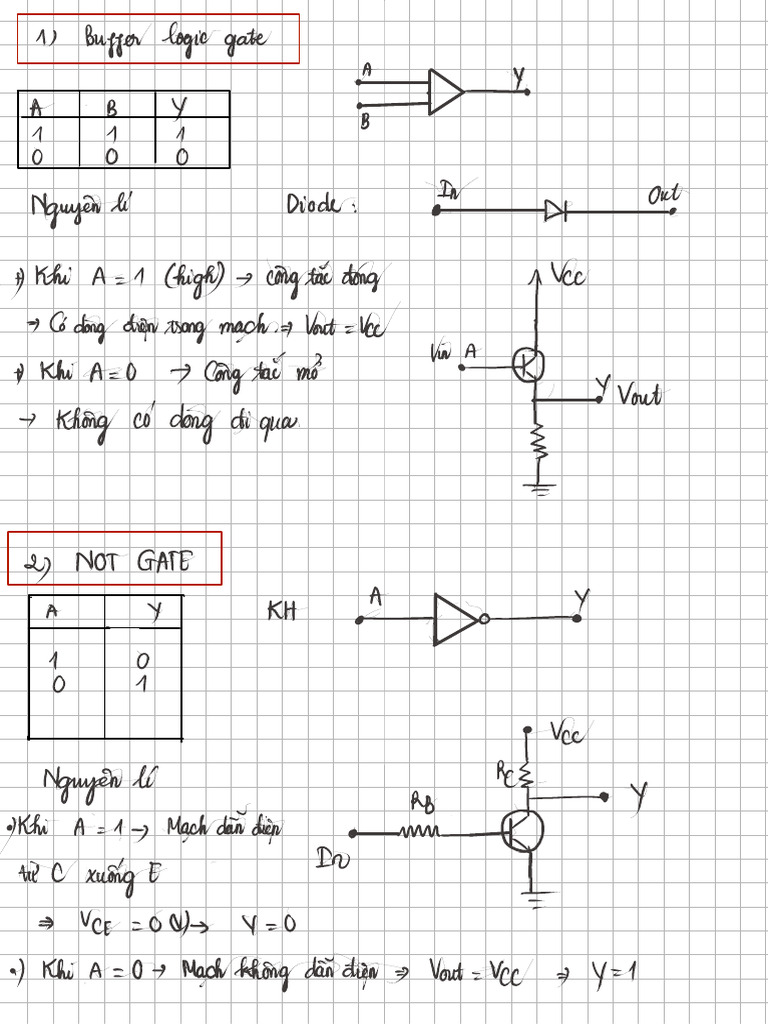

Logic Gate Pdf In this chapter, we explore the basic principles and design of cmos digital logic gates, starting with the simplest gate, the inverter, and expanding to more complex gates such as nand,. Gate input controls whether current can flow between the other two terminals or not. Eee 591 captainknowledge15944 1 21 2025 lecture 6 logic gate basics.pdf view full document. Review: logic circuit delay • for cmos (or almost all logic circuit families), only one fundamental equation necessary to determine delay: dv i c = dt Δ.

Examples Of Cmos Logic Gates Filled Pdf Eee 591 captainknowledge15944 1 21 2025 lecture 6 logic gate basics.pdf view full document. Review: logic circuit delay • for cmos (or almost all logic circuit families), only one fundamental equation necessary to determine delay: dv i c = dt Δ. Able to apply mathematical methods and transistor physics in the analysis of cmos circuits and design cmos inverter with different loads for given levels noise margins and propagation delay’s. The circuit that drives will use a t gate to connect to the bus with a low impedance path. all other circuits that aren’t driving will switch their t gates to be a high impedance. Static cmos circuit at every point in time (except during the switching transients) each gate output is connected to either v or v dd ss via a low resistive path the outputs of the gates assume at all times the value of the boolean function, implemented by the circuit. The four terminals of a fet (gate, source, drain and bulk) connect to conducting surfaces that generate a complicated set of electric fields in the channel region which depend on the relative voltages of each terminal.

Lecture 6 Logic Gate Basics Pdf Logic Gate Cmos Able to apply mathematical methods and transistor physics in the analysis of cmos circuits and design cmos inverter with different loads for given levels noise margins and propagation delay’s. The circuit that drives will use a t gate to connect to the bus with a low impedance path. all other circuits that aren’t driving will switch their t gates to be a high impedance. Static cmos circuit at every point in time (except during the switching transients) each gate output is connected to either v or v dd ss via a low resistive path the outputs of the gates assume at all times the value of the boolean function, implemented by the circuit. The four terminals of a fet (gate, source, drain and bulk) connect to conducting surfaces that generate a complicated set of electric fields in the channel region which depend on the relative voltages of each terminal.

Comments are closed.