Labview Code Stream High Speed Data Between Fpga And Pc With A Dma Fifo Walk Through

Receive High Speed Adc Output Data With Labview Fpga Ni Community Developer walk through for the "fpga pc dma fifo" labview project available for download at learn cf.ni teach riodevg that covers this topic: "efficiently transfer blocks. Efficiently transfer blocks of data between the pc and fpga by direct memory access (dma) first in first out (fifo) buffers. connect your academic rio device to your pc using usblan, ethernet, or wi fi. note: not all academic rio devices have ethernet and wi fi connectivity options.

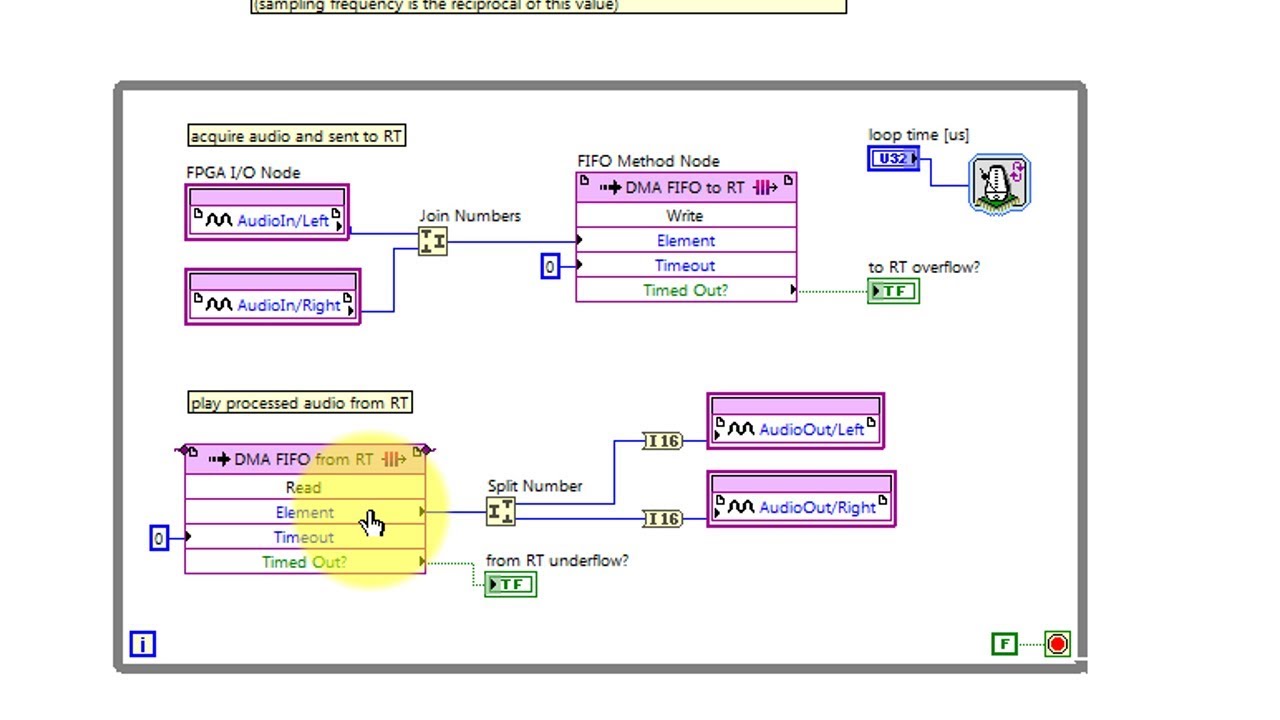

Receive High Speed Adc Output Data With Labview Fpga Ni Community If you're sometimes seeing a number of elements to read >0 after you fail to read an element, most likely the data is moved into the fpga fifo buffer between the read and the check for the number of elements to read. In general, use programmatic front panel communication for small, frequent data transfers and dma for streaming large amounts of data at a time. use user defined i o variables for transferring coherent sets of fpga i o data to and from an rt host vi. Labview has built in functions for transferring data between the fpga and the real time processor within the compactrio system. choose from more than 600 built in labview functions to build your multithreaded embedded system for real time control, analysis, data logging, and communication. This example demonstrates how to use dma fifos to send data to and from an fpga target (bidirectional data transfer). this project is configured to work with a pxi 7841r on a windows computer, but this same code will work on any fpga target and a windows or a real time host.

Labview Fpga的dma Fifo问题 Ni Community Labview has built in functions for transferring data between the fpga and the real time processor within the compactrio system. choose from more than 600 built in labview functions to build your multithreaded embedded system for real time control, analysis, data logging, and communication. This example demonstrates how to use dma fifos to send data to and from an fpga target (bidirectional data transfer). this project is configured to work with a pxi 7841r on a windows computer, but this same code will work on any fpga target and a windows or a real time host. Direct memory access (dma) is a fifo based method of transferring data between an fpga target and the host computer. dma does not involve the host processor; therefore, it is the fastest available method for transferring large amounts of data between the fpga target and the host. Operating instructions and expected results for the "fpga pc dma fifo" labview project available for download at learn cf.ni teach riodevg that covers this topic:. Fpga read write is asynchronous and you can’t determine when a value is read written. e.g. use read for latest value. but if you want to stream data (lossless) use a fifo. dma fifo is great for ensuring access to each item sent. Transfer data, commands, and status between the fpga target and a host system (rt or pc). describes programmatic front panel communication and direct memory access (dma) communication.

Solved Labview Fpga Code Execution Speed Ni Community Direct memory access (dma) is a fifo based method of transferring data between an fpga target and the host computer. dma does not involve the host processor; therefore, it is the fastest available method for transferring large amounts of data between the fpga target and the host. Operating instructions and expected results for the "fpga pc dma fifo" labview project available for download at learn cf.ni teach riodevg that covers this topic:. Fpga read write is asynchronous and you can’t determine when a value is read written. e.g. use read for latest value. but if you want to stream data (lossless) use a fifo. dma fifo is great for ensuring access to each item sent. Transfer data, commands, and status between the fpga target and a host system (rt or pc). describes programmatic front panel communication and direct memory access (dma) communication.

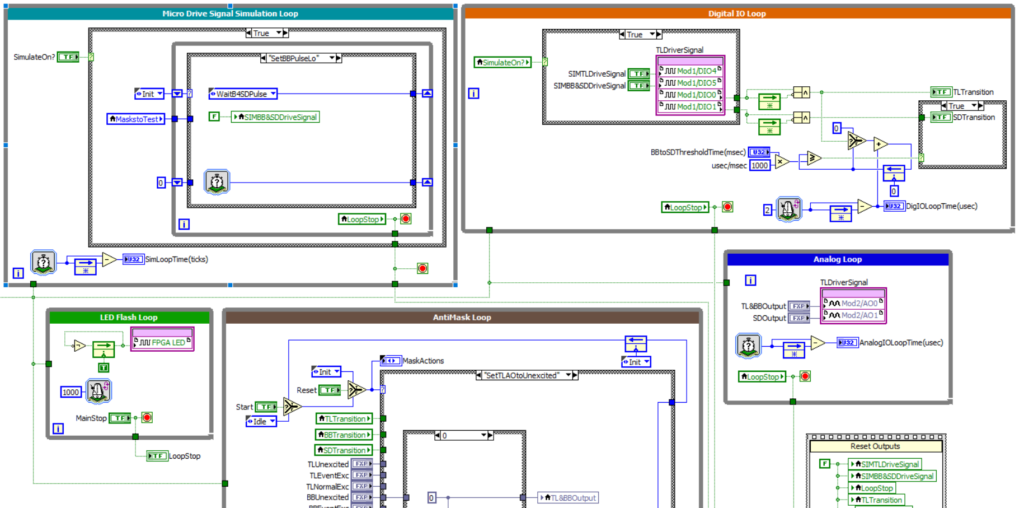

Labview Fpga Code Viewpoint Systems Fpga read write is asynchronous and you can’t determine when a value is read written. e.g. use read for latest value. but if you want to stream data (lossless) use a fifo. dma fifo is great for ensuring access to each item sent. Transfer data, commands, and status between the fpga target and a host system (rt or pc). describes programmatic front panel communication and direct memory access (dma) communication.

Generating Labview Fpga Code Digital Filter Design To Vrogue Co

Comments are closed.