Instruction Level Parallelism

Instruction Level Parallelism Pdf Parallel Computing Central Instruction level parallelism (ilp) refers to the capability of a processor to execute multiple instructions at the same time. instead of running each instruction strictly one after another, ilp uses hardware and compiler techniques to overlap instruction execution wherever dependencies allow. Learn about the concepts, techniques, and challenges of instruction level parallelism (ilp) in computer architecture. explore how ilp can be exploited by hardware and software, and how it differs from pipelining and general parallel processing.

Instruction Level Parallelism Pdf Central Processing Unit Cpu Cache Learn about the concepts and techniques of instruction level parallelism, machine parallelism, and multiple issue processors. explore the challenges and solutions of dependencies, resource conflicts, and speculation in vliw and superscalar processors. Learn about the concept, techniques and applications of instruction level parallelism (ilp), the parallel or simultaneous execution of a sequence of instructions in a computer program. compare and contrast ilp with concurrency, dynamic and static parallelism, and micro architectural techniques such as pipelining, superscalar execution, out of order execution, and speculative execution. Learn about instruction level parallelism (ilp), a measure of the average number of instructions in a program that can be executed at the same time. explore the concepts of superpipelining, superscalar, and multiple issue processors, and how they extract ilp and resolve hazards. N taken 3.1 ilp: concepts and challenges instruction level parallelism (ilp): overlap the executi. erage dynamic branch frequency 15% to 25% 3 to 6 . strs execute between a pair of branches. plus instruct. ns in bb likely to depend on each other. to obtain substantial performance enhancements. we must expl.

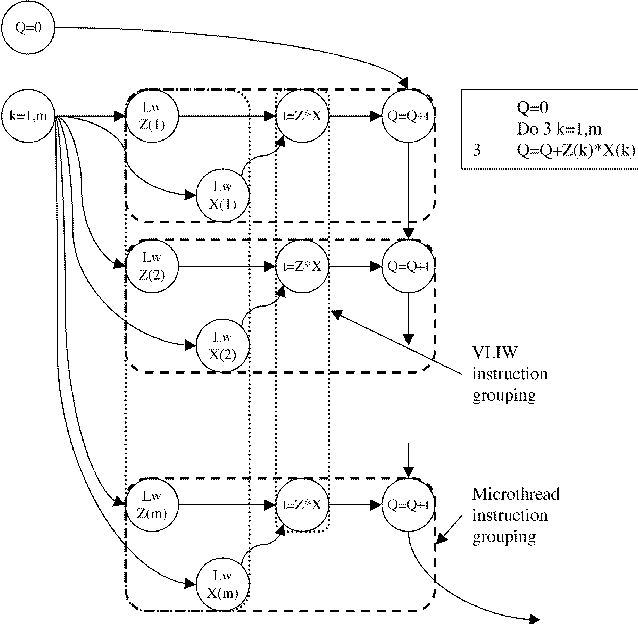

Lecture 17 Mips Instruction Level Parallelism Pdf Parallel Learn about instruction level parallelism (ilp), a measure of the average number of instructions in a program that can be executed at the same time. explore the concepts of superpipelining, superscalar, and multiple issue processors, and how they extract ilp and resolve hazards. N taken 3.1 ilp: concepts and challenges instruction level parallelism (ilp): overlap the executi. erage dynamic branch frequency 15% to 25% 3 to 6 . strs execute between a pair of branches. plus instruct. ns in bb likely to depend on each other. to obtain substantial performance enhancements. we must expl. Learn how modern cpus use pipelining, superscalar execution, and out of order processing to improve performance and efficiency. find out how to program for instruction level parallelism and avoid common pitfalls. There are two approaches to exploiting ilp. 1. static technique – software dependent. 2. dynamic technique – hardware dependent. the simplest and most common way to increase the amount of parallelism is loop level parallelism. here is a simple example of a loop, which adds two 1000 element arrays, that is completely parallel:. Ocw is open and available to the world and is a permanent mit activity. Instruction level parallelism (ilp) ilp: the simultaneous execution of multiple instructions from a program. while pipelining is a form of ilp, the general application of ilp goes much further into more aggressive techniques to achieve parallel execution of the instructions in the instruction stream.

Instruction Level Parallelism Semantic Scholar Learn how modern cpus use pipelining, superscalar execution, and out of order processing to improve performance and efficiency. find out how to program for instruction level parallelism and avoid common pitfalls. There are two approaches to exploiting ilp. 1. static technique – software dependent. 2. dynamic technique – hardware dependent. the simplest and most common way to increase the amount of parallelism is loop level parallelism. here is a simple example of a loop, which adds two 1000 element arrays, that is completely parallel:. Ocw is open and available to the world and is a permanent mit activity. Instruction level parallelism (ilp) ilp: the simultaneous execution of multiple instructions from a program. while pipelining is a form of ilp, the general application of ilp goes much further into more aggressive techniques to achieve parallel execution of the instructions in the instruction stream.

Instruction Level Parallelism Semantic Scholar Ocw is open and available to the world and is a permanent mit activity. Instruction level parallelism (ilp) ilp: the simultaneous execution of multiple instructions from a program. while pipelining is a form of ilp, the general application of ilp goes much further into more aggressive techniques to achieve parallel execution of the instructions in the instruction stream.

Instruction Level Parallelism Pptx

Comments are closed.