Improving The Sram Layout Design Using Cadence Virtuoso

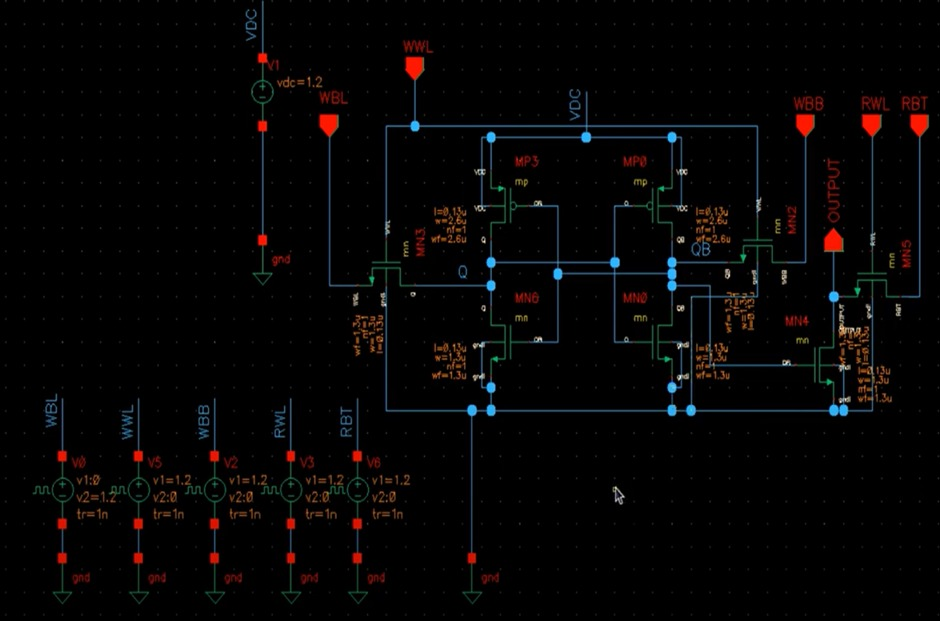

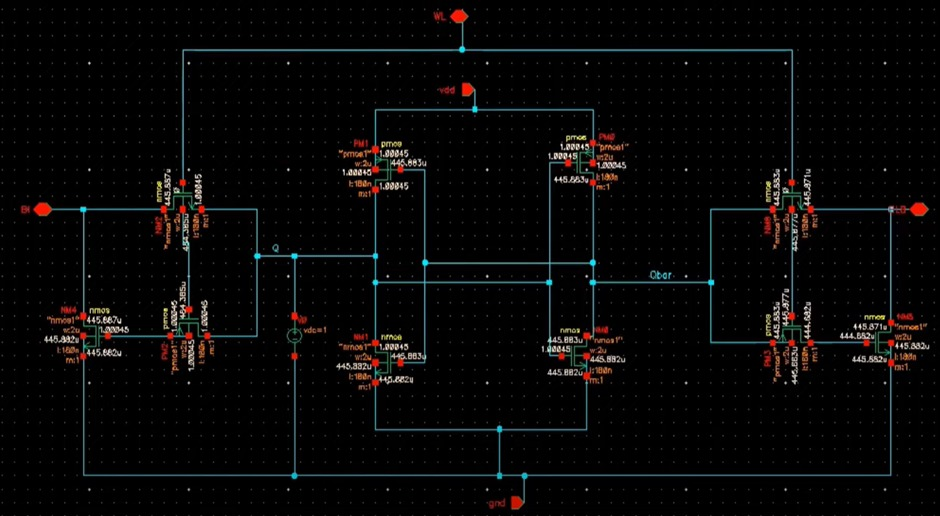

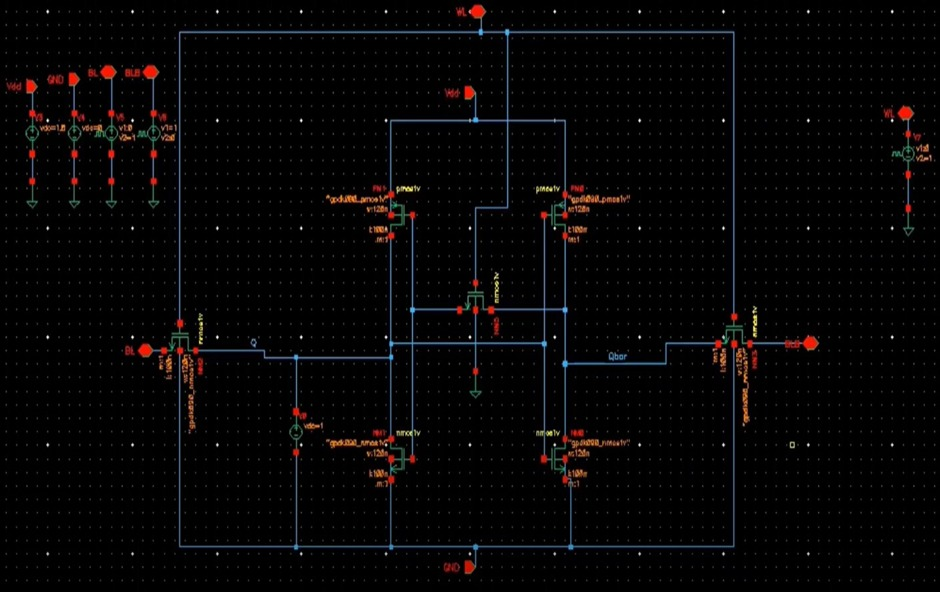

Improving The Sram Layout Design Using Cadence Virtuoso This paper introduces an optimized method for sram layout design with cadence virtuoso for 6t, 7t, 8t, and 10t sram cells to improve their performance in power constrained and high speed applications. This paper introduces an optimized method for sram layout design with cadence virtuoso for 6t, 7t, 8t, and 10t sram cells to improve their performance in power constrained and.

Improving The Sram Layout Design Using Cadence Virtuoso This project presents the design, layout, and comparative analysis of 6t, 7t, and 8t static random access memory (sram) cells. the cells were designed in cadence virtuoso using a 180nm cmos technology. This work presents the complete design, simulation, and layout verification of a low power 6t sram cell using 180nm cmos technology in the cadence virtuoso environment. Abstract—this project presents the design and implementation of a static random access memory (sram) system using the cadence virtuoso. sram is a key component in modern digital systems, particularly in cache memory, due to its high speed, low latency, and low static power consumption. This paper presents design and implementation of 4 t and 6 t sram cell using different cmos technology and simulated using cadence virtuoso across three cmos technology nodes: 180 nm, 90 nm, and 45 nm. the study is purely simulation based with layout implemented to obtain accurate area estimations.

Improving The Sram Layout Design Using Cadence Virtuoso Abstract—this project presents the design and implementation of a static random access memory (sram) system using the cadence virtuoso. sram is a key component in modern digital systems, particularly in cache memory, due to its high speed, low latency, and low static power consumption. This paper presents design and implementation of 4 t and 6 t sram cell using different cmos technology and simulated using cadence virtuoso across three cmos technology nodes: 180 nm, 90 nm, and 45 nm. the study is purely simulation based with layout implemented to obtain accurate area estimations. Dual threshold 7t sram cell is proposed and compared with the standard 6t sram cell. it analyses the basis of read delay, write delay, leakage power consumption and static noise margin in all the three (hold, read and write) mode of operation. As part of my digital vlsi design course, i developed a 1 kilobyte (32×32) 6t sram array from schematic to layout using cadence virtuoso. this included designing and verifying memory cells, integrating a 5 to 32 decoder for wordline selection, and optimizing the layout for performance and area. 🎓 welcome to this complete tutorial on 6t sram cell design using cadence virtuoso with gpdk 45nm technology. in this video, you’ll learn how to design, simulate, and analyze a 6t sram. Sram is used widely because of its huge storage capacity and can be accessed in less time with low power consumption. this paper presents design and implementation of 16bit 6t sram using different cmos technologies using cadence virtuoso tool.

Improving The Sram Layout Design Using Cadence Virtuoso Dual threshold 7t sram cell is proposed and compared with the standard 6t sram cell. it analyses the basis of read delay, write delay, leakage power consumption and static noise margin in all the three (hold, read and write) mode of operation. As part of my digital vlsi design course, i developed a 1 kilobyte (32×32) 6t sram array from schematic to layout using cadence virtuoso. this included designing and verifying memory cells, integrating a 5 to 32 decoder for wordline selection, and optimizing the layout for performance and area. 🎓 welcome to this complete tutorial on 6t sram cell design using cadence virtuoso with gpdk 45nm technology. in this video, you’ll learn how to design, simulate, and analyze a 6t sram. Sram is used widely because of its huge storage capacity and can be accessed in less time with low power consumption. this paper presents design and implementation of 16bit 6t sram using different cmos technologies using cadence virtuoso tool.

Comments are closed.