How Cpus Store And Load Data Building Data Memory In Logisim Mips Cpu Tutorial

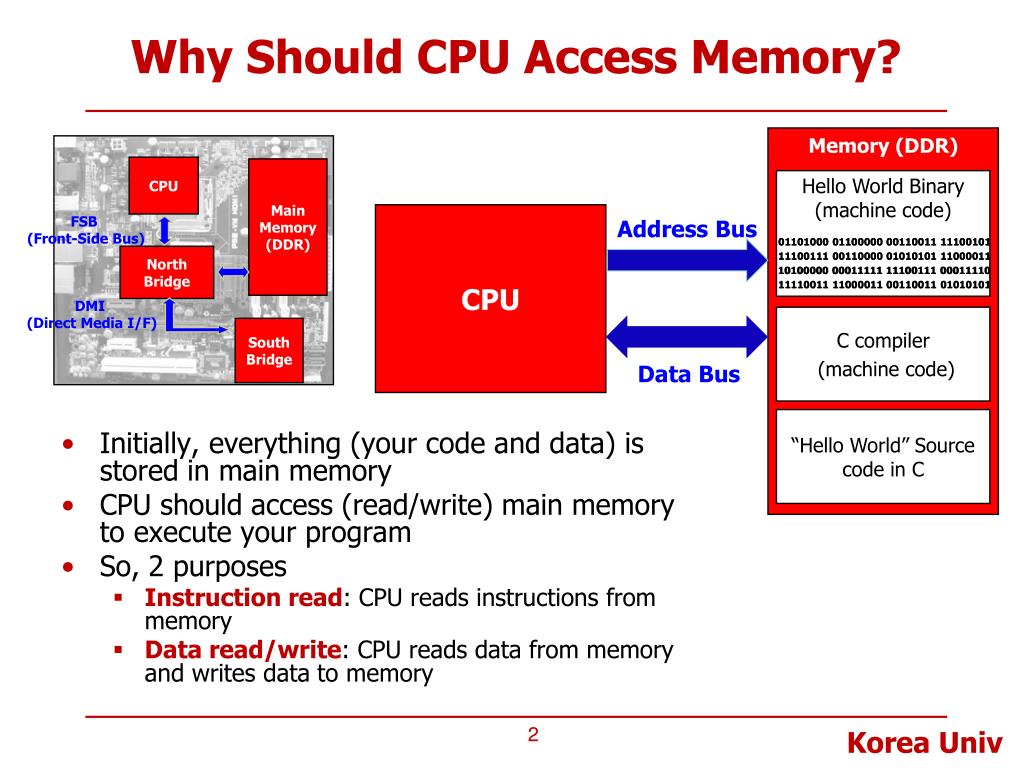

Ppt Chap 2 Instructions Language Of The Computer Powerpoint You’ll learn how memory is addressed, how to control writes using the `memwrite` signal, and how to simulate both load and store operations with ease. 🔧 topics covered:. This top level circuit connects the program counter, instruction memory, control unit, register file, alu, and data memory into a datapath capable of executing mips instructions.

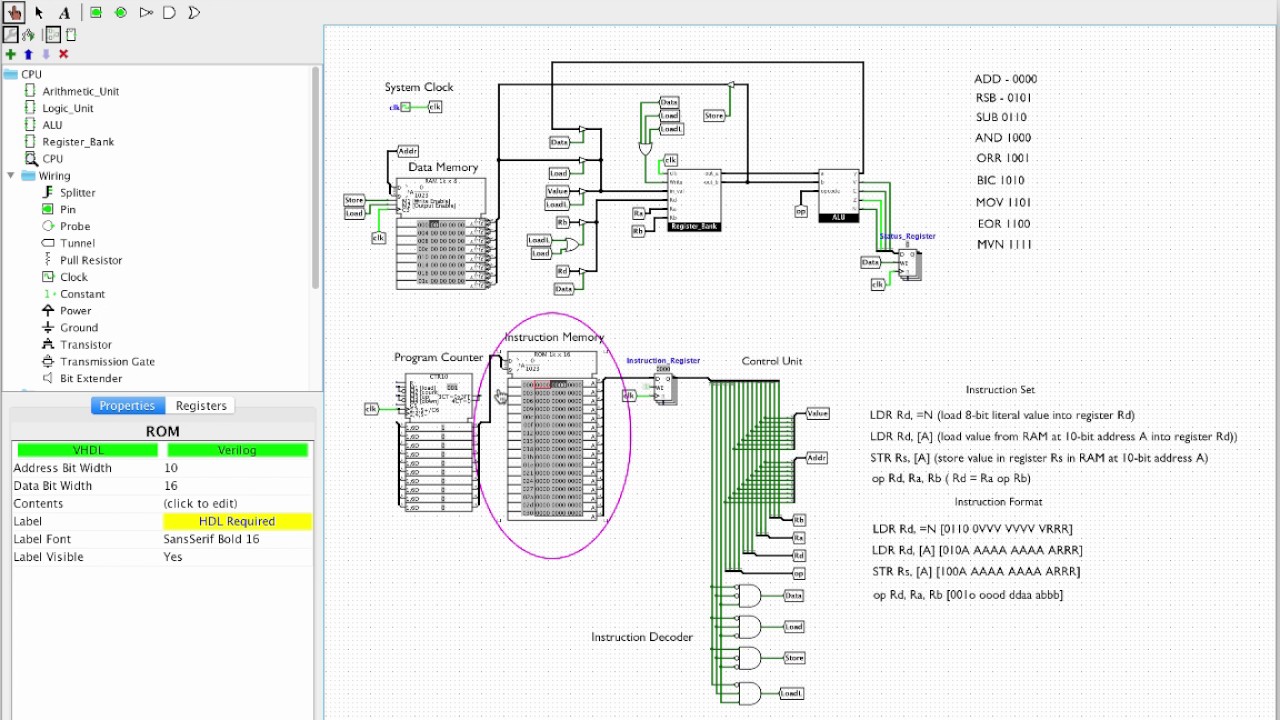

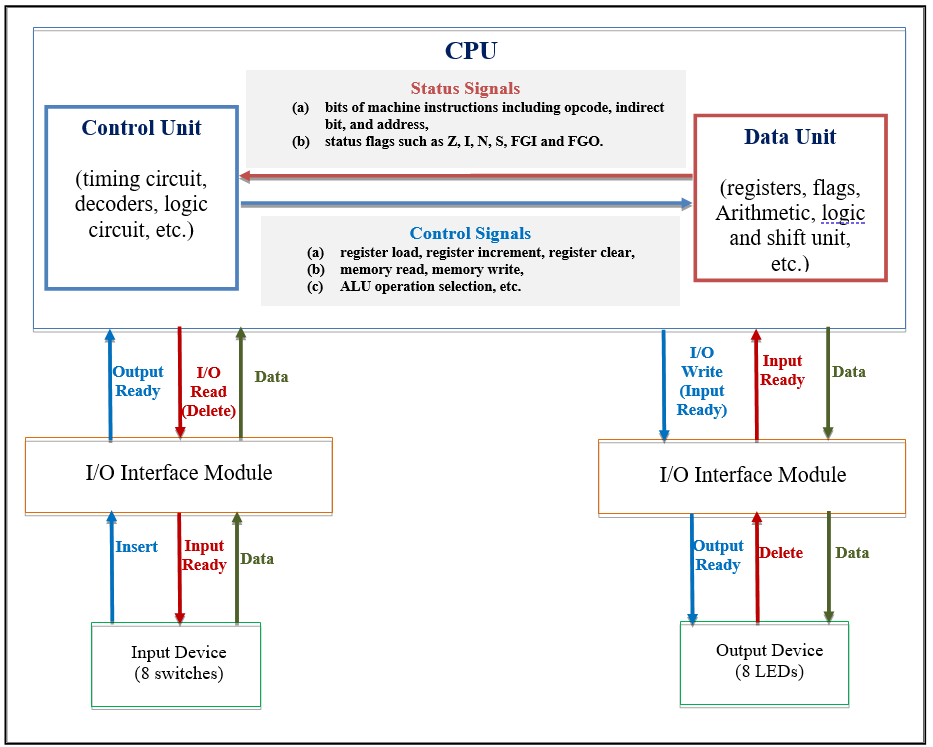

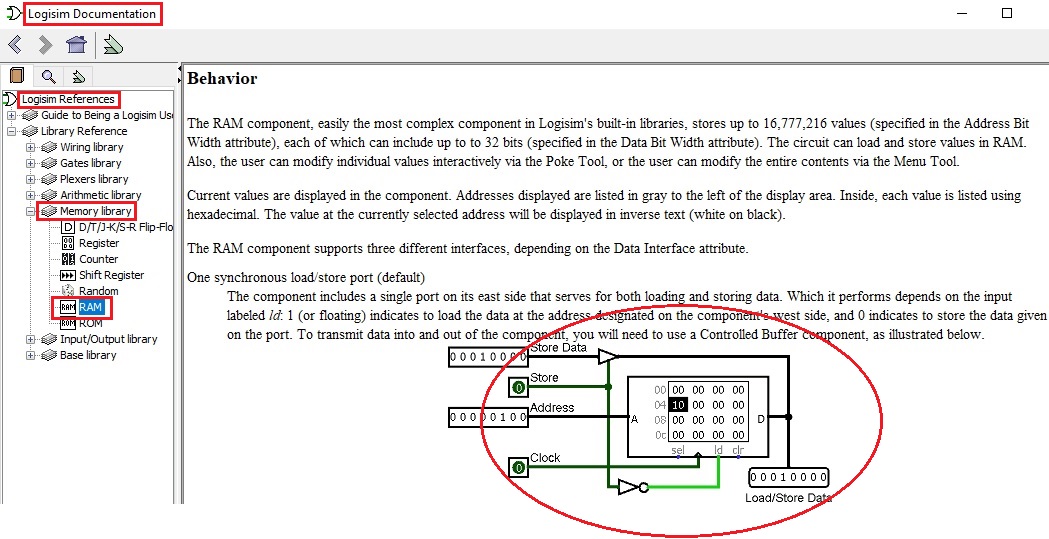

Cpu Simulation In Logisim Youtube In this project you will complete the design of your mips processor by adding most of the remaining mips instructions. your basic execution loop from the previous project should contain most of the major components, with the exception of ram for the load store instructions. The mem step is where the data memory (dmem) can be modified using data store instructions or read using data load instructions. since the addi instruction does not need accesss to dmem, we can ignore this part of the circuit for now and continue with the next step of execution. This project is a single cycle mips 32 processor built from the ground up in logisim. the goal was to demonstrate a clear, pedagogical datapath while still achieving full functional correctness across the core mips instruction set. All the circuits we’ve designed throughout the series: the alu, register file, program counter, instruction memory, data memory, and control unit are now integrated into a fully working cpu.

Task 3 Complete Logisim Design Of The Cpu Full Chegg This project is a single cycle mips 32 processor built from the ground up in logisim. the goal was to demonstrate a clear, pedagogical datapath while still achieving full functional correctness across the core mips instruction set. All the circuits we’ve designed throughout the series: the alu, register file, program counter, instruction memory, data memory, and control unit are now integrated into a fully working cpu. Note that the common components in src common are shared among the cpus, and must be present in the same folder as the cpu circ file for it to work. the main and most feature rich version is the pipelined cpu with operand forwarding, which will be referred to as mips cpu in the rest of this readme. A collection of step by step tutorials on core digital logic topics like alu, register files, adders, and cpu architecture using mips and logisim. This repository demonstrates the design and functionality of a 32 bit mips processor using logisim evolution. it includes both a single cycle processor and a pipelined processor to cater to different learning needs. A complete mips (microprocessor without interlocked pipeline stages) processor implementation using logisim circuit simulation. this project demonstrates both basic and advanced processor architectures with memory integration.

8 Bit Cpu Note that the common components in src common are shared among the cpus, and must be present in the same folder as the cpu circ file for it to work. the main and most feature rich version is the pipelined cpu with operand forwarding, which will be referred to as mips cpu in the rest of this readme. A collection of step by step tutorials on core digital logic topics like alu, register files, adders, and cpu architecture using mips and logisim. This repository demonstrates the design and functionality of a 32 bit mips processor using logisim evolution. it includes both a single cycle processor and a pipelined processor to cater to different learning needs. A complete mips (microprocessor without interlocked pipeline stages) processor implementation using logisim circuit simulation. this project demonstrates both basic and advanced processor architectures with memory integration.

16 Bit Cpu Design In Logisim Fpga4student This repository demonstrates the design and functionality of a 32 bit mips processor using logisim evolution. it includes both a single cycle processor and a pipelined processor to cater to different learning needs. A complete mips (microprocessor without interlocked pipeline stages) processor implementation using logisim circuit simulation. this project demonstrates both basic and advanced processor architectures with memory integration.

Ppt Lecture 8 Mips Instructions 2 Memory Access Load Store

Comments are closed.