Github Zadielerick Fpga Power Side Channel Attack Implementation And

Power Side Channel Attack On Software Implemented Aes Embedded Systems Implementation and defense against fpga based remote power side channel attack zadielerick fpga power side channel attack. Implementation and defense against fpga based remote power side channel attack fpga power side channel attack data at main · zadielerick fpga power side channel attack.

Power Side Channel Attack On Software Implemented Aes Embedded Systems Implementation and defense against fpga based remote power side channel attack fpga power side channel attack rsa algorithm at main · zadielerick fpga power side channel attack. Implementation and defense against fpga based remote power side channel attack releases · zadielerick fpga power side channel attack. Implementation and defense against fpga based remote power side channel attack pulse · zadielerick fpga power side channel attack. Attacks based on side channel analysis (sca) pose a severe security threat to modern computing platforms, further exacerbated on iot devices by their pervasiveness and handling of private and critical data.

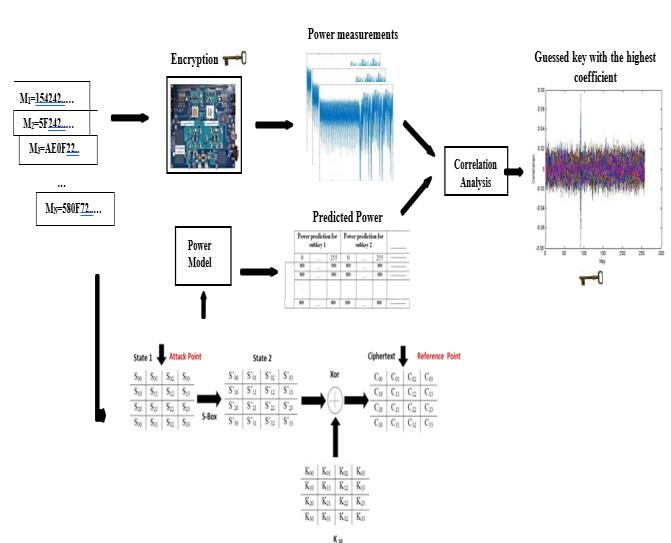

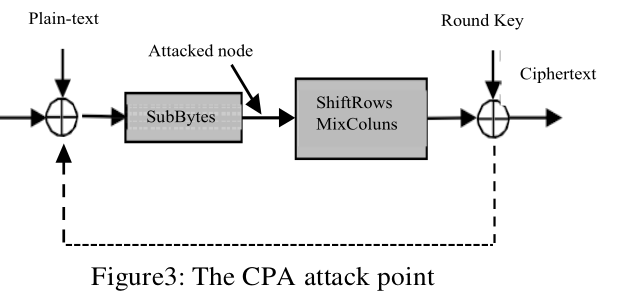

Side Channel Attack Setup For Power Leakage Based Evaluations Implementation and defense against fpga based remote power side channel attack pulse · zadielerick fpga power side channel attack. Attacks based on side channel analysis (sca) pose a severe security threat to modern computing platforms, further exacerbated on iot devices by their pervasiveness and handling of private and critical data. This paper introduces a framework that combines deep learning (dl) models and dynamic partial reconfiguration (dpr) in field programmable gate arrays (fpga) to mitigate side channel attacks. The rapid adoption of heterogeneous computing has driven the integration of field programmable gate arrays (fpgas) into cloud datacenters and flexible system on. Rsa has been repeatedly given as an example of an algorithm that is susceptible to power side channels, but is this a common exploitable property? does real world code often have parts that could be taken advantage of by monitoring power?. This paper introduces a framework that combines deep learning (dl) models and dynamic partial reconfiguration (dpr) in field programmable gate arrays (fpga) to mitigate side channel attacks (sca).

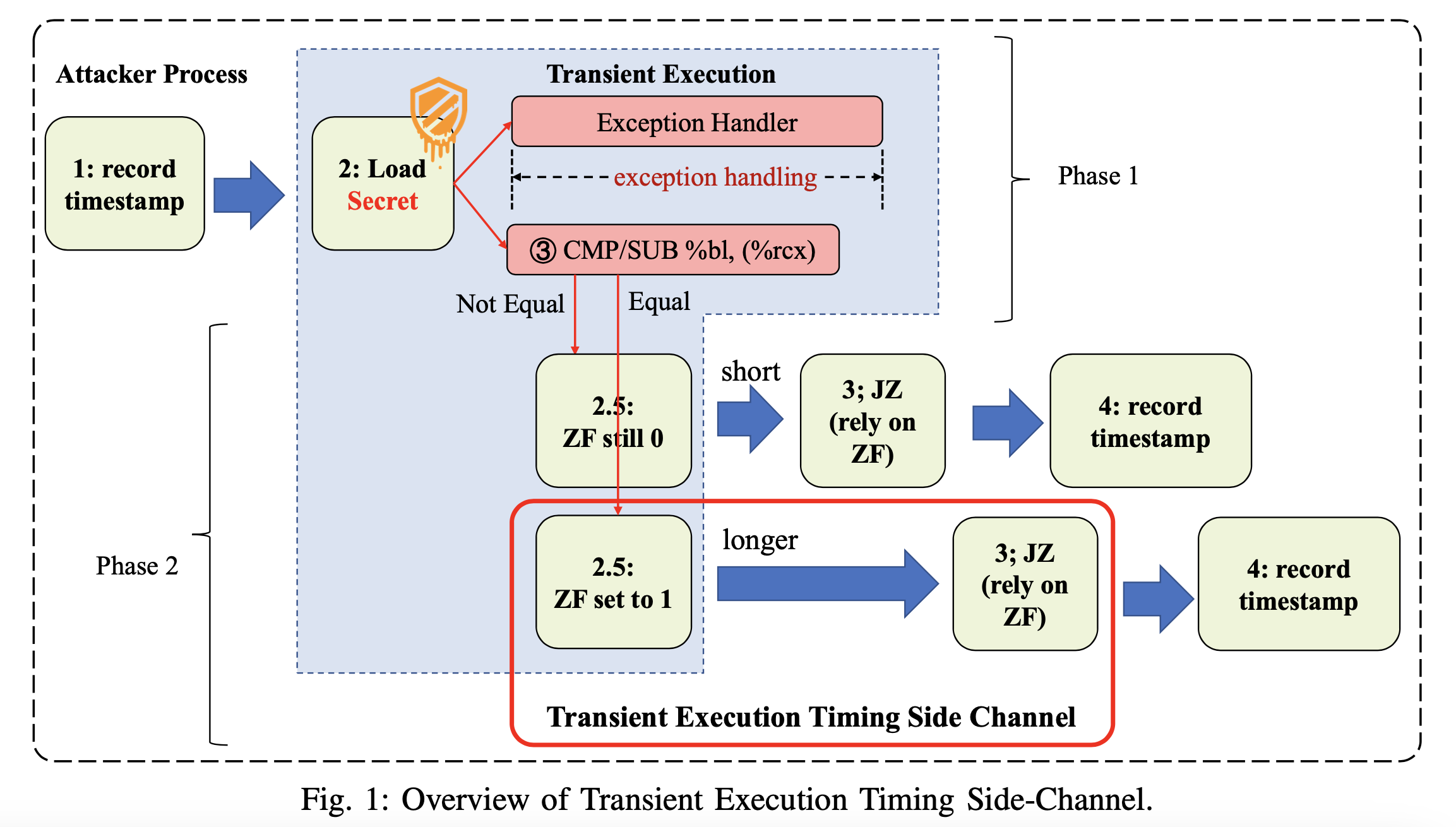

Researchers Discover New Side Channel Attack That Works Against Intel This paper introduces a framework that combines deep learning (dl) models and dynamic partial reconfiguration (dpr) in field programmable gate arrays (fpga) to mitigate side channel attacks. The rapid adoption of heterogeneous computing has driven the integration of field programmable gate arrays (fpgas) into cloud datacenters and flexible system on. Rsa has been repeatedly given as an example of an algorithm that is susceptible to power side channels, but is this a common exploitable property? does real world code often have parts that could be taken advantage of by monitoring power?. This paper introduces a framework that combines deep learning (dl) models and dynamic partial reconfiguration (dpr) in field programmable gate arrays (fpga) to mitigate side channel attacks (sca).

Comments are closed.