Github Ibrahimhamada Pipelined Arm Processor Using System Verilog

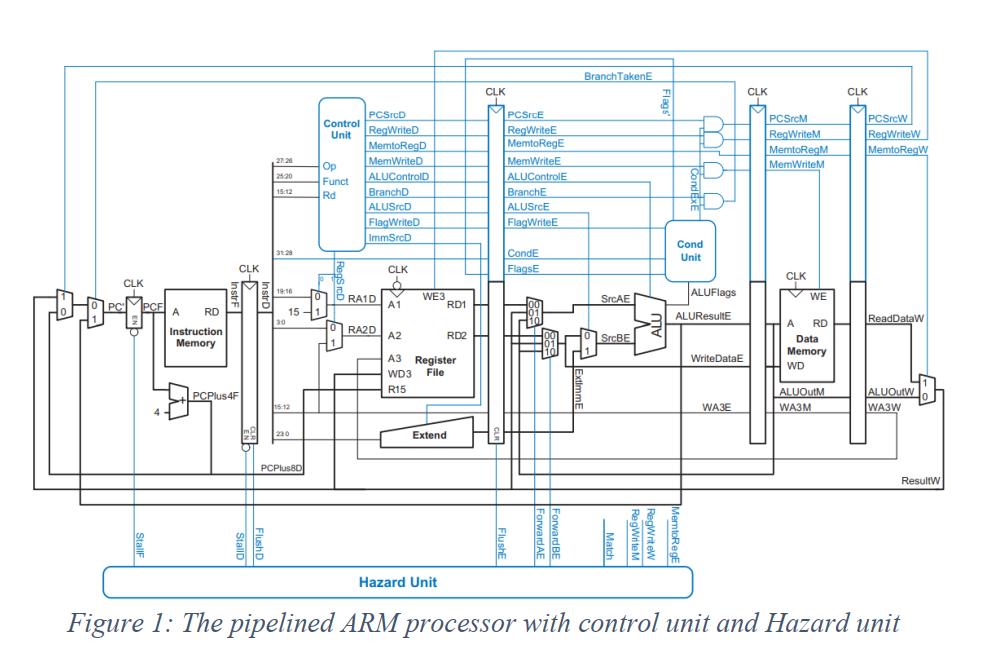

Github Ibrahimhamada Pipelined Arm Processor Using System Verilog The processor should support the following instructions: 1) data processing instructions where the second source can be either an immediate value or a source register, with no shifts. The project aims to implement the pipelined arm processor using system verilog with a hazard unit. my project of the computer architecture and assembly language course offered in fall 2021 @ zewail city.

Github Ibrahimhamada Pipelined Arm Processor Using System Verilog The project aims to implement the pipelined arm processor using system verilog with a hazard unit. my project of the computer architecture and assembly language course offered in fall 2021 @ zewail city. The project aims to implement the pipelined arm processor using system verilog with a hazard unit. releases · ibrahimhamada pipelined arm processor using system verilog. The project aims to implement the pipelined arm processor using system verilog with a hazard unit. actions · ibrahimhamada pipelined arm processor using system verilog. The project aims to implement the pipelined arm processor using system verilog with a hazard unit. pipelined arm processor using system verilog presentation.pdf at main · ibrahimhamada pipelined arm processor using system verilog.

Github Doniagameel Pipelined Processor Using Verilog Harvard The project aims to implement the pipelined arm processor using system verilog with a hazard unit. actions · ibrahimhamada pipelined arm processor using system verilog. The project aims to implement the pipelined arm processor using system verilog with a hazard unit. pipelined arm processor using system verilog presentation.pdf at main · ibrahimhamada pipelined arm processor using system verilog. The proposed processor is a 5 stage pipelined design based on the risc v (rv32i) architecture, implemented using verilog hdl. the design follows the principle of instruction pipelining, where multiple instructions are executed in an overlapped manner different stages. Dynamic pipeline scheduling allow the cpu to execute instructions out of order to avoid stalls but commit result to registers in order example. Essor and a pipeline processor using verilog. we simulated our modules using xilinx ise and verifi d that our two models did behave as expected. the two processors can perform basic r, i, j type mips instructions correctly and the pipeline processor is abl. Please enable javascript to view the page content. your support id is: 2306051617274535189.

Github Shivpvtel Five Stage Pipelined Cpu Verilog The proposed processor is a 5 stage pipelined design based on the risc v (rv32i) architecture, implemented using verilog hdl. the design follows the principle of instruction pipelining, where multiple instructions are executed in an overlapped manner different stages. Dynamic pipeline scheduling allow the cpu to execute instructions out of order to avoid stalls but commit result to registers in order example. Essor and a pipeline processor using verilog. we simulated our modules using xilinx ise and verifi d that our two models did behave as expected. the two processors can perform basic r, i, j type mips instructions correctly and the pipeline processor is abl. Please enable javascript to view the page content. your support id is: 2306051617274535189.

Comments are closed.