Github Anayk2004 4bitparitygenerator 4bitparitygenerator

Github Anayk2004 4bitparitygenerator 4bitparitygenerator 4bitparitygenerator. contribute to anayk2004 4bitparitygenerator development by creating an account on github. To implement a 4 bit parity generator circuit, use xor gates to sequentially combine the input bits. the final xor gate output is the parity bit. here is the process to implement the 4 bit parity generator: connect input bits a and b to the first xor gate. connect input bits c and d to the second xor gate.

Github Girinath Nu Verilog 4bit Comparator Github For this purpose, we have two digital circuits namely, parity generator and parity checker. both these circuits help us to detect and correct any kind of error in transmitted data. read this chapter to learn the basics of parity generator and parity checker, along with their types and applications. Specifically, it discusses implementing even and odd parity generators using reversible logic gates to reduce information loss and delay. it provides the circuit diagram output of the 4 bit parity generator and checker built. the project helped develop skills in digital circuits and error detection for data transmission. Below is the even parity generator circuit diagram for a 3 bit data. data bits are represented by label 20, 21, 22 and the parity bit is represented with label 31. Parity generator and checker project overview this project implements a parity generator and parity checker using verilog. parity generator: generates an even parity bit for a 4 bit input data. parity checker: checks the received data along with the parity bit to detect single bit errors.

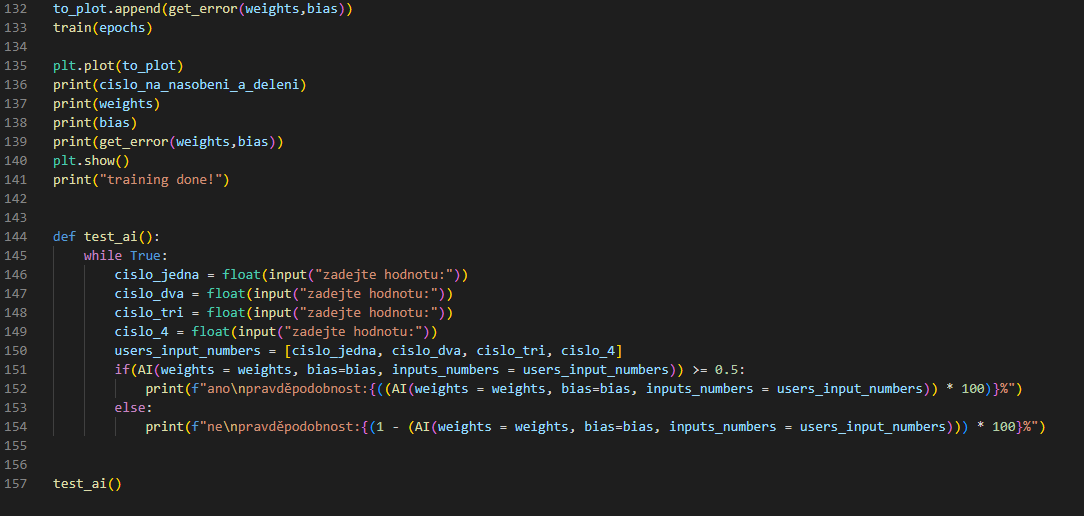

Github Aizej Ai For 4bit Inputs From Scratch Flashback To 2021 When Below is the even parity generator circuit diagram for a 3 bit data. data bits are represented by label 20, 21, 22 and the parity bit is represented with label 31. Parity generator and checker project overview this project implements a parity generator and parity checker using verilog. parity generator: generates an even parity bit for a 4 bit input data. parity checker: checks the received data along with the parity bit to detect single bit errors. The 4 bit parity generator is a digital circuit designed to compute the parity bit for a 4 bit input data. it generates either an even or odd parity bit, depending on the configuration. this parity bit is used for error detection in data transmission or storage, ensuring data integrity. A 4 bit parity generator is a combinational logic circuit that computes the parity bit for a 4 bit input. it outputs a single bit indicating whether the total number of 1s in the input is odd (odd parity) or even (even parity). This project focuses on a 4 bit parity generator, which computes the parity bit for a 4 bit input data sequence. features: parity generation: generates even or odd parity for a 4 bit input. configurable logic: easily modifiable to switch between even and odd parity schemes. 4bitparitygenerator. contribute to anayk2004 4bitparitygenerator development by creating an account on github.

Comments are closed.