Github Abhirathsujith Switchlevelmodellingnand Verilog

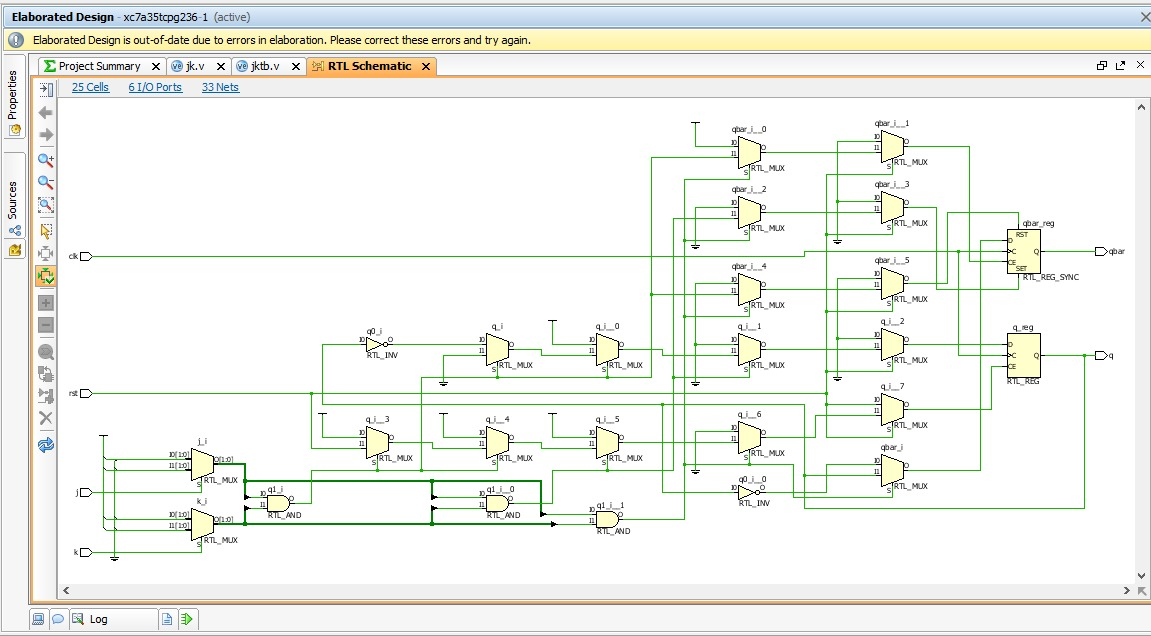

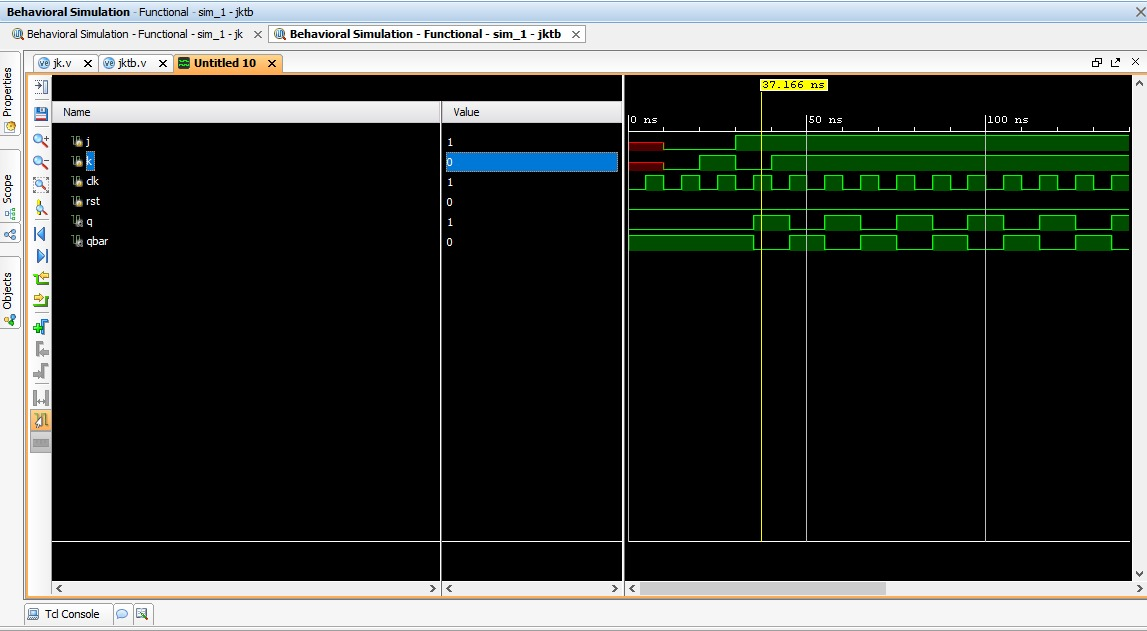

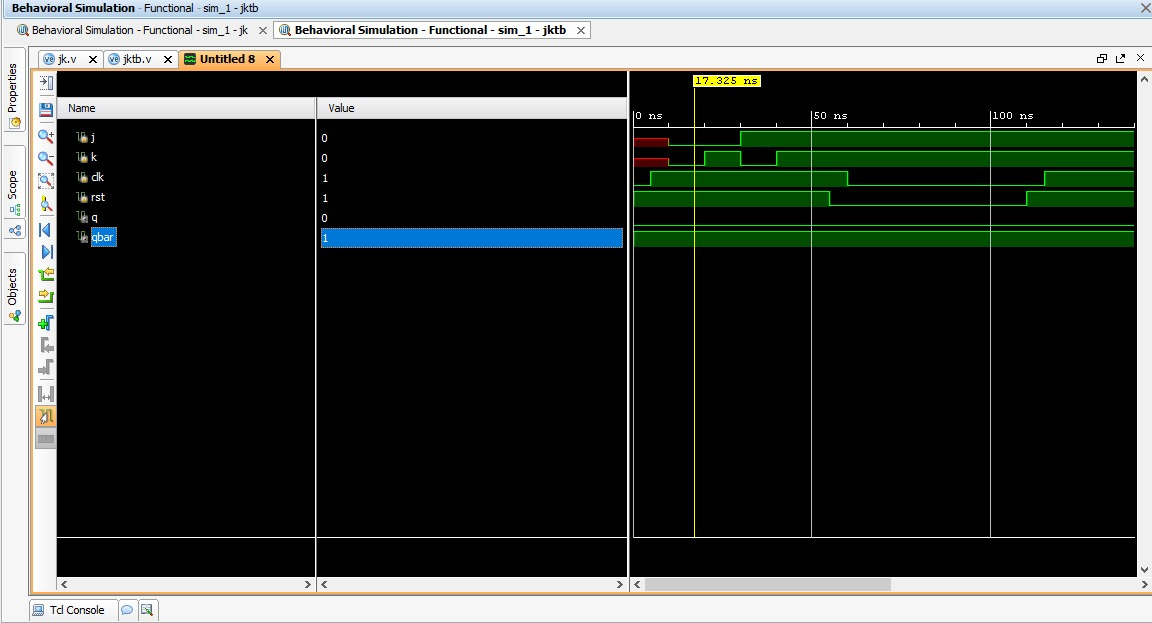

Github Abhirathsujith Jkff Verilog Jkff In Verilog Contribute to abhirathsujith switchlevelmodellingnand verilog development by creating an account on github. Contribute to abhirathsujith switchlevelmodellingnor verilog development by creating an account on github.

Github Abhirathsujith Jkff Verilog Jkff In Verilog Switchlevelmodellingnand verilog. contribute to abhirathsujith switchlevelmodellingnand verilog development by creating an account on github. Github is where people build software. more than 100 million people use github to discover, fork, and contribute to over 420 million projects. Github is where people build software. more than 100 million people use github to discover, fork, and contribute to over 330 million projects. Switchlevelmodellingnand verilog. contribute to abhirathsujith switchlevelmodellingnand verilog development by creating an account on github.

Github Abhirathsujith Jkff Verilog Jkff In Verilog Github is where people build software. more than 100 million people use github to discover, fork, and contribute to over 330 million projects. Switchlevelmodellingnand verilog. contribute to abhirathsujith switchlevelmodellingnand verilog development by creating an account on github. Switchlevelmodellingnand verilog. contribute to abhirathsujith switchlevelmodellingnand verilog development by creating an account on github. Switchlevelmodellingnand verilog. contribute to abhirathsujith switchlevelmodellingnand verilog development by creating an account on github. Svunit is an open source test framework for asic and fpga developers writing verilog systemverilog code. tools, frameworks, ip cores, libraries and more!. I am experimenting with how the “pullup” and “bufif0” switch level constructs work in verilog. the concept is to be used in an uvm based i2c top module for generating the “sda” and “scl” signals.

Github Abhirathsujith Lfsr Verilog Lfsr Verilog Switchlevelmodellingnand verilog. contribute to abhirathsujith switchlevelmodellingnand verilog development by creating an account on github. Switchlevelmodellingnand verilog. contribute to abhirathsujith switchlevelmodellingnand verilog development by creating an account on github. Svunit is an open source test framework for asic and fpga developers writing verilog systemverilog code. tools, frameworks, ip cores, libraries and more!. I am experimenting with how the “pullup” and “bufif0” switch level constructs work in verilog. the concept is to be used in an uvm based i2c top module for generating the “sda” and “scl” signals.

Github Abhirathsujith Demux Verilog Demux In Verilog Svunit is an open source test framework for asic and fpga developers writing verilog systemverilog code. tools, frameworks, ip cores, libraries and more!. I am experimenting with how the “pullup” and “bufif0” switch level constructs work in verilog. the concept is to be used in an uvm based i2c top module for generating the “sda” and “scl” signals.

Comments are closed.