Gate It 2004 Solved Question On Average Memory Access Time

Average Memory Access Time Download Scientific Diagram In this video, i have solved a question on memory access time which has been asked in gate 2004. #gate preparation #coa #memory access time if you have any doubts ask me in the. Access times of level 1 cache, level 2 cache and main memory are 1 n s, 10 n s, and 500 n s respectively. the hit rates of level 1 and level 2 caches are 0.8 and 0.9, respectively.

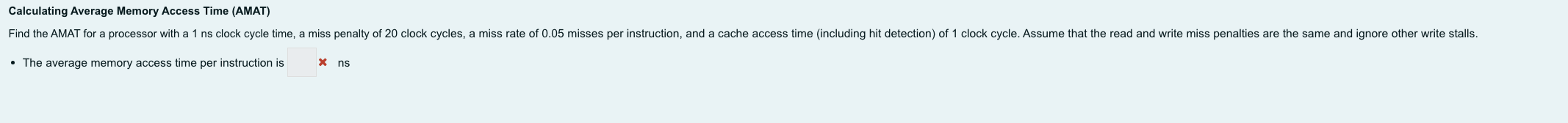

Solved Calculating Average Memory Access Time Amat The Chegg What is the average access time of the system ignoring the search time within the cache?. Suppose we run dijkstra’s single source shortest path algorithm on the following edge weighted directed graph with vertex p as the source. in what order do the nodes get included into the set of vertices for which the shortest path distances are finalized?. Cache is a small, fast memory between the cpu and ram — it exploits temporal and spatial locality to reduce average access time address breakdown: offset (block offset) index (set number) tag — always verify these add up to total address bits. The memory access time is 1 nanosecond for a read operation with a hit in cache, 5 nanoseconds for a read operation with a miss in cache, 2 nanoseconds for a write operation with a hit in cache and 10 nanoseconds for a write operation with a miss in cache.

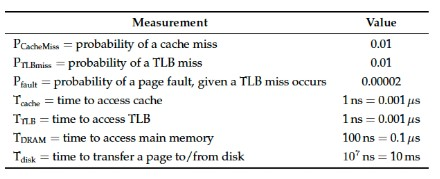

Average Memory Access Time And Energy Download Scientific Diagram Cache is a small, fast memory between the cpu and ram — it exploits temporal and spatial locality to reduce average access time address breakdown: offset (block offset) index (set number) tag — always verify these add up to total address bits. The memory access time is 1 nanosecond for a read operation with a hit in cache, 5 nanoseconds for a read operation with a miss in cache, 2 nanoseconds for a write operation with a hit in cache and 10 nanoseconds for a write operation with a miss in cache. Practice gate cse cache memory previous year questions with detailed solutions. topic wise pyqs on mapping techniques, hit ratio and cache performance. In this session vishvadeep gothi will discuss all formulas for calculating average or effective memory access time from subjects coa and os with practice questions. • since demand paging like caching, can compute average access time! (“effective access time”) – this is a slowdown by a factor of 40! • what if want slowdown by less than 10%? – this is about 1 page fault in 400,000! what factors lead to misses in page cache? – how might we remove these misses? » need to predict future somehow! more later. We need to calculate the performance of cache design for a byte addressed memory system. the type of the cache design is a direct mapped cache (dm) with four blocks, each block holding one four byte word.

Detailed Average Memory Access Time Download Scientific Diagram Practice gate cse cache memory previous year questions with detailed solutions. topic wise pyqs on mapping techniques, hit ratio and cache performance. In this session vishvadeep gothi will discuss all formulas for calculating average or effective memory access time from subjects coa and os with practice questions. • since demand paging like caching, can compute average access time! (“effective access time”) – this is a slowdown by a factor of 40! • what if want slowdown by less than 10%? – this is about 1 page fault in 400,000! what factors lead to misses in page cache? – how might we remove these misses? » need to predict future somehow! more later. We need to calculate the performance of cache design for a byte addressed memory system. the type of the cache design is a direct mapped cache (dm) with four blocks, each block holding one four byte word.

Question What Is The Average Memory Access Time The Chegg • since demand paging like caching, can compute average access time! (“effective access time”) – this is a slowdown by a factor of 40! • what if want slowdown by less than 10%? – this is about 1 page fault in 400,000! what factors lead to misses in page cache? – how might we remove these misses? » need to predict future somehow! more later. We need to calculate the performance of cache design for a byte addressed memory system. the type of the cache design is a direct mapped cache (dm) with four blocks, each block holding one four byte word.

Comments are closed.