Full Adder Using Half Adder Verilog Code Vlsi Verilog Fulladder

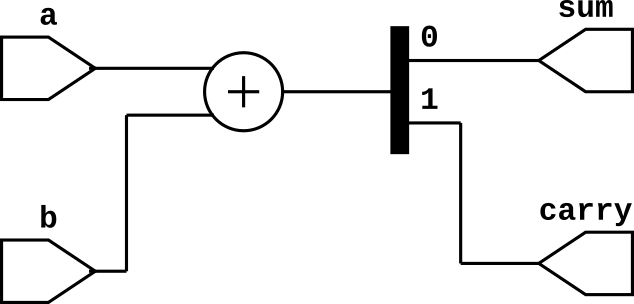

Full Adder Verilog Code Siliconvlsi For a half adder, s u m = a ⊕ b and c a r r y = a b hence, we can implement full adder using two half adder with addition of one or gate. first, we'll describe a half adder by creating a module half adder in verilog source file. below is the verilog code for half adder. ); assign sum = a ^ b; assign carry = a & b; endmodule. In this post we are going to share with you the full adder verilog code using two half adders. the verilog code of full adder using two half adder and one or gate is shown below. in above code we used gate level modeling along with instantiation. the above full adder code can be written in data flow model as shown below.

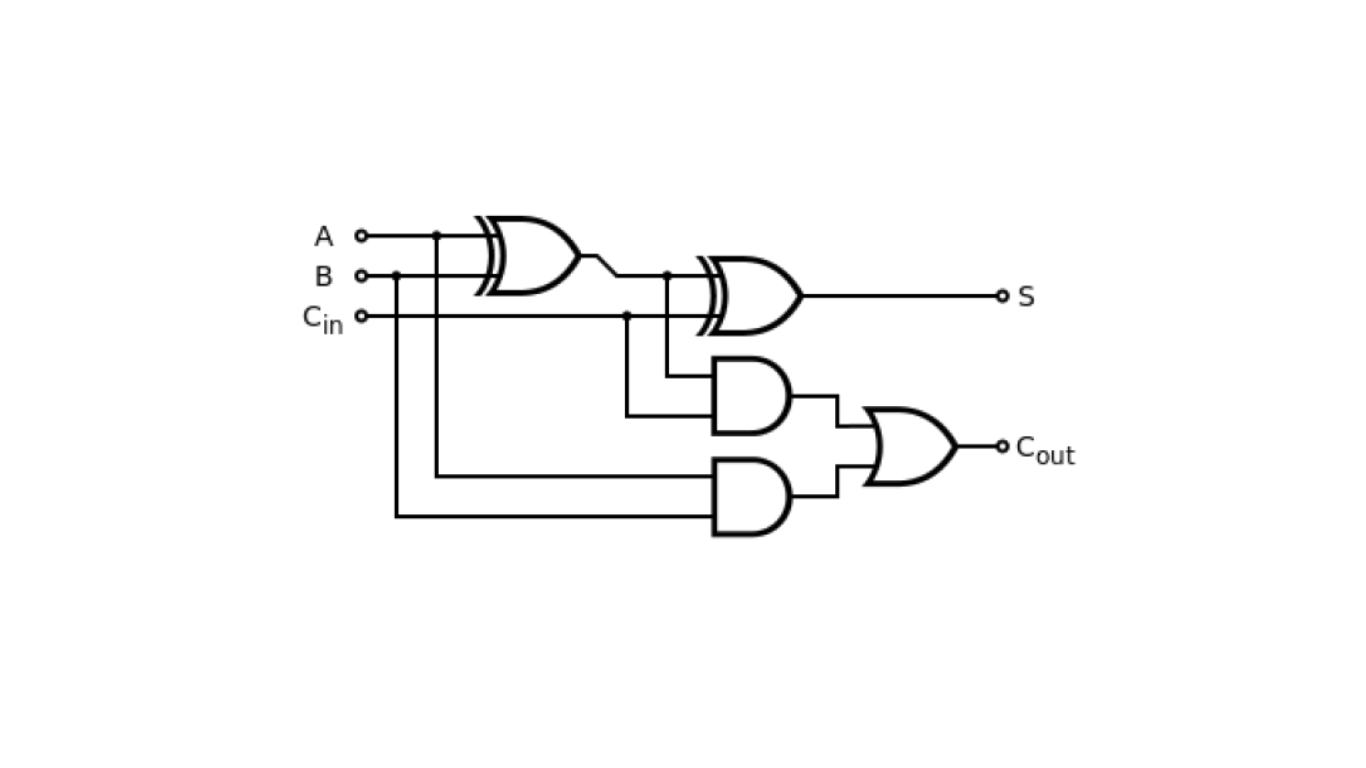

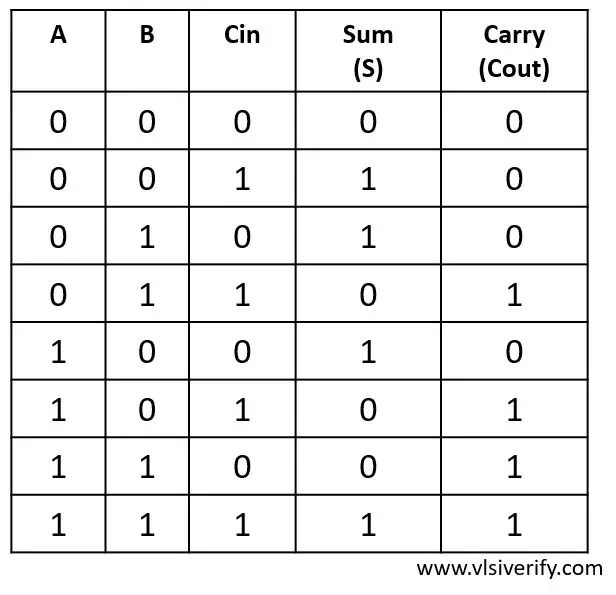

Full Adder Verilog Code Siliconvlsi However, full adder can also be designed using two half adders. the full adder adds three single bit input and produce two single bit output. thus, it is useful when an extra carry bit is available from the previously generated result. Full adder is a combinational circuit that performs binary addition. the block diagram of a full adder is given below, in which a in, b in and c in are the inputs and sum out and carry out are. A full adder adds three input bits, to give out, two output bits sum and carry. they have the following truth table: a full adder can be implemented using two half adders and one two input or gate. so what is a half adder? a half adder adds two inputs bits, to give one sum and one carry output bit. To obtain a full adder from a half adder we take the first two inputs and add them and use the sum and carry outputs and the third input to get the final sum and carry output of the full adder. in this article, we will explore half adders, and full adders and implement full adders using half adders.

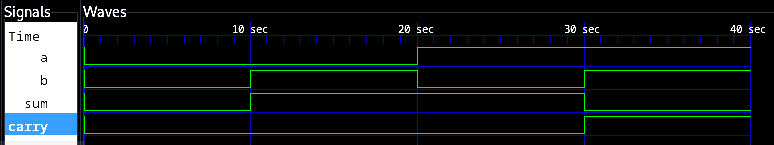

Full Adder Vlsi Verify A full adder adds three input bits, to give out, two output bits sum and carry. they have the following truth table: a full adder can be implemented using two half adders and one two input or gate. so what is a half adder? a half adder adds two inputs bits, to give one sum and one carry output bit. To obtain a full adder from a half adder we take the first two inputs and add them and use the sum and carry outputs and the third input to get the final sum and carry output of the full adder. in this article, we will explore half adders, and full adders and implement full adders using half adders. The goal of this lab was to work with verilog code in rtl design using intel quartus prime and vivado applications. the primary focus was implementing half adder and full adder designs using verilog and verifying their functionality through rtl design and simulation. Edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web browser. Vlsi design, verilog code, vhdl code. Learn how to design half adder, full adder, and carry ripple adder in verilog and systemverilog. add binary numbers with these digital circuits.

Full Adder Vlsi Verify The goal of this lab was to work with verilog code in rtl design using intel quartus prime and vivado applications. the primary focus was implementing half adder and full adder designs using verilog and verifying their functionality through rtl design and simulation. Edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web browser. Vlsi design, verilog code, vhdl code. Learn how to design half adder, full adder, and carry ripple adder in verilog and systemverilog. add binary numbers with these digital circuits.

Half Adder Verilog Code Circuit Fever Vlsi design, verilog code, vhdl code. Learn how to design half adder, full adder, and carry ripple adder in verilog and systemverilog. add binary numbers with these digital circuits.

Half Adder Verilog Code Circuit Fever

Comments are closed.