Fpga Based Hw Acceleration

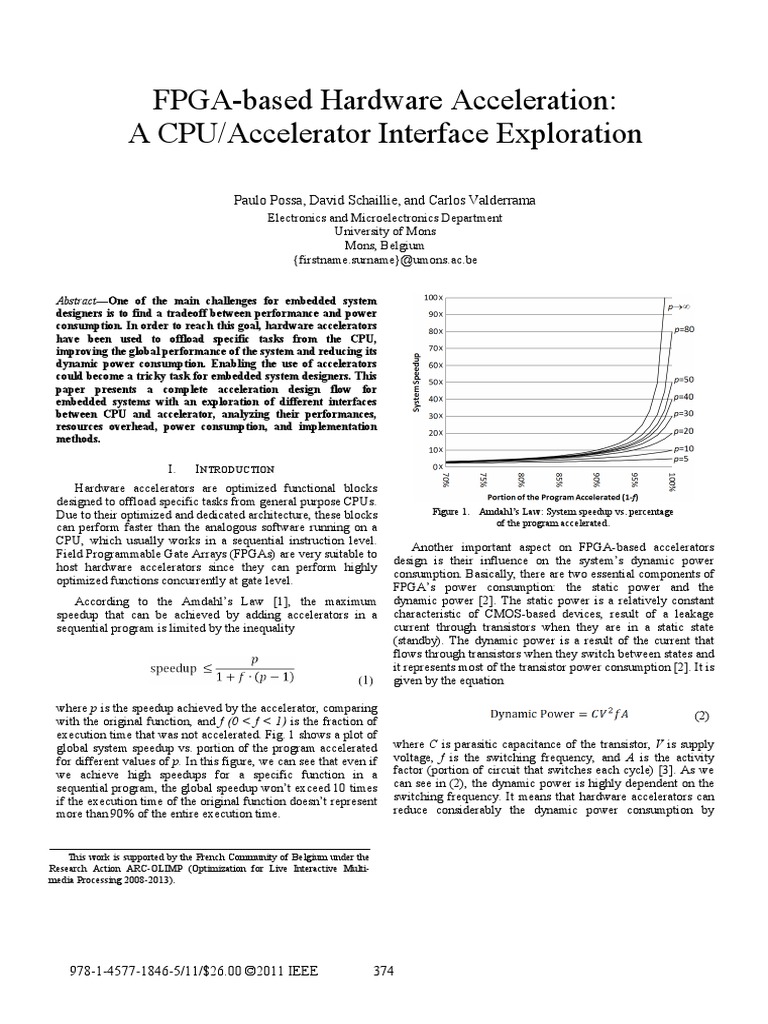

Fpga Based Hardware Acceleration A Cpu Accelerator Interface Dive into advanced techniques for hardware acceleration in fpga based systems, including optimization strategies and design best practices. Fpga acceleration : boosting application performance without acceleration fpga handles compute intensive, deeply pipelined, massively parallel operations. cpu handles the rest.

Fpga H W Ips And Acceleration Bigzetta Bigzetta A tech blog on fpga design by jeff johnson — tutorials, reference designs and resources for fpga developers. Fpga processing can be fast, but when hw sw partitioning is used we also have to keep in mind the bandwidth of communication between cpu ram and fpga. transfer time of the array from ram to fpga is dominant!. In this study, we proposed a novel end to end fpga based acceleration system that supports native sql statements and storage engine. we defined a callback process to reload the database query logic and customize the scanning method for database queries. In this paper, a novel rc architecture is proposed that provides the exact same instruction set that a standard general purpose risc microprocessor (e.g., arm cortex m0) has while automating the generation of a tightly coupled rc component to improve system performance.

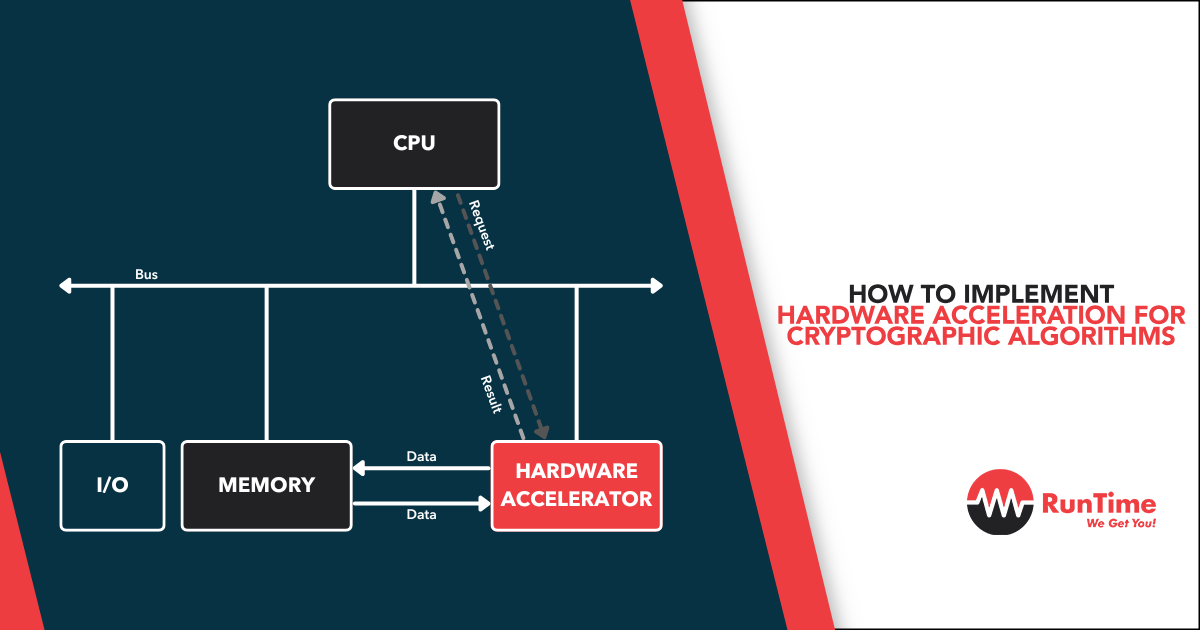

Fpga Based Hardware Acceleration For Cryptography In this study, we proposed a novel end to end fpga based acceleration system that supports native sql statements and storage engine. we defined a callback process to reload the database query logic and customize the scanning method for database queries. In this paper, a novel rc architecture is proposed that provides the exact same instruction set that a standard general purpose risc microprocessor (e.g., arm cortex m0) has while automating the generation of a tightly coupled rc component to improve system performance. This work proposed hardware adam (hw adam), an efficient fixed point accelerator for adam highlighting hardware oriented mathematical optimizations. hw adam has two designs: efficient adam (e adam) unit reduced the hardware resource consumption by around 90% compared with the related work. This review paper aims to analyze, compare, and discuss different approaches to implementing network based hardware accelerators in fpga and programmable soc (systems on chip). We present a detailed overview of the opencl framework integration and the fpga based hardware acceleration framework for k means algorithm optimization. furthermore, this implementation can be fully realized without the need for hardware description language (hdl) code. This research delves into hardware acceleration using fpgas to overcome these constraints, offering a novel approach to expedite machine learning algorithms. traditional software implementations of machine learning algorithms often fall short in meeting real time processing requirements.

Github Jedibobo Fpga Hw Acceleration Social Disatancing Monitor This work proposed hardware adam (hw adam), an efficient fixed point accelerator for adam highlighting hardware oriented mathematical optimizations. hw adam has two designs: efficient adam (e adam) unit reduced the hardware resource consumption by around 90% compared with the related work. This review paper aims to analyze, compare, and discuss different approaches to implementing network based hardware accelerators in fpga and programmable soc (systems on chip). We present a detailed overview of the opencl framework integration and the fpga based hardware acceleration framework for k means algorithm optimization. furthermore, this implementation can be fully realized without the need for hardware description language (hdl) code. This research delves into hardware acceleration using fpgas to overcome these constraints, offering a novel approach to expedite machine learning algorithms. traditional software implementations of machine learning algorithms often fall short in meeting real time processing requirements.

Fpga Hardware Acceleration And Design Services For Hft Velvetech We present a detailed overview of the opencl framework integration and the fpga based hardware acceleration framework for k means algorithm optimization. furthermore, this implementation can be fully realized without the need for hardware description language (hdl) code. This research delves into hardware acceleration using fpgas to overcome these constraints, offering a novel approach to expedite machine learning algorithms. traditional software implementations of machine learning algorithms often fall short in meeting real time processing requirements.

Pdf Hw Acceleration For Fpga Based Drive Controllers

Comments are closed.