Four Bit Synchronous Binary Counter

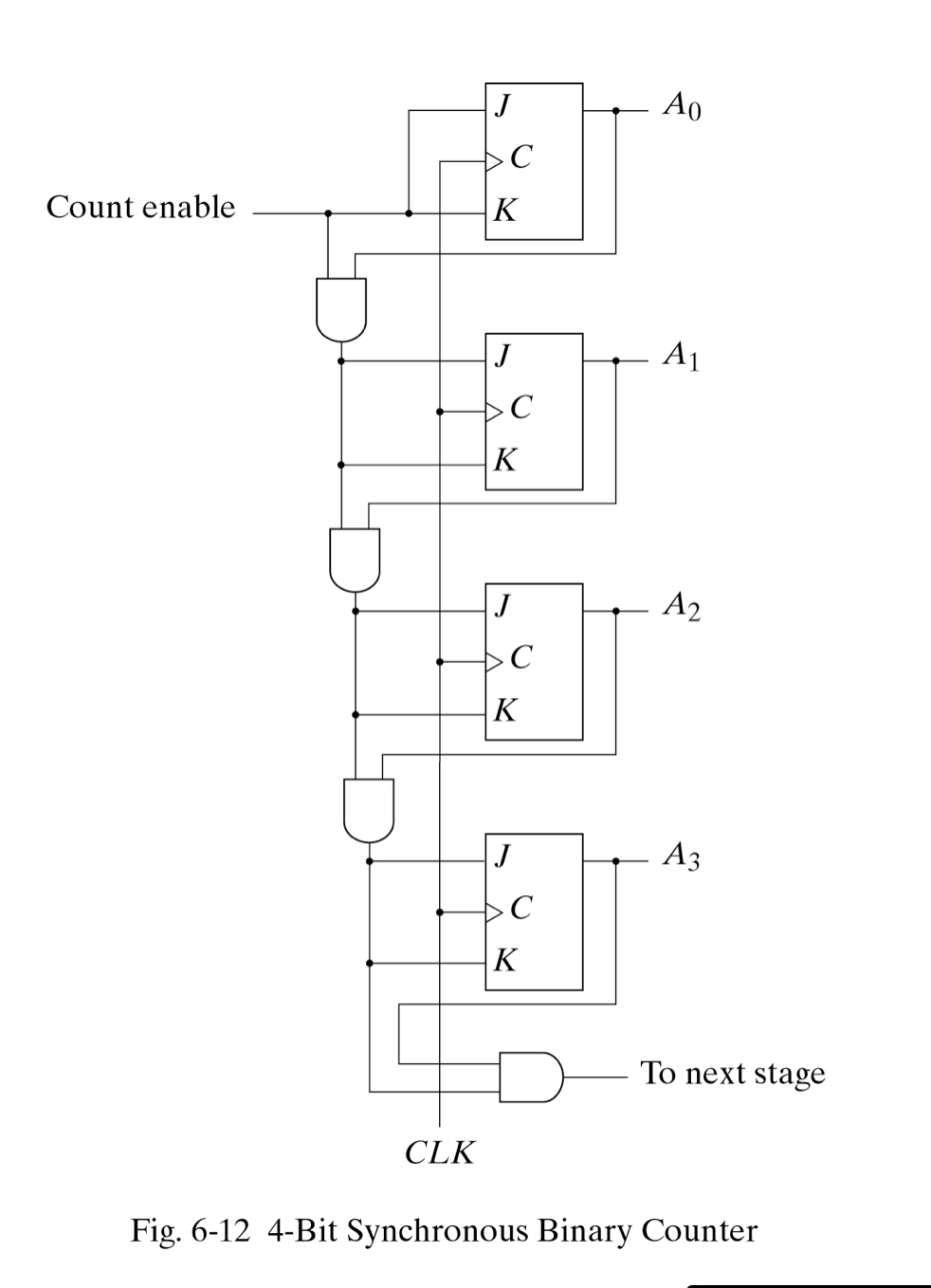

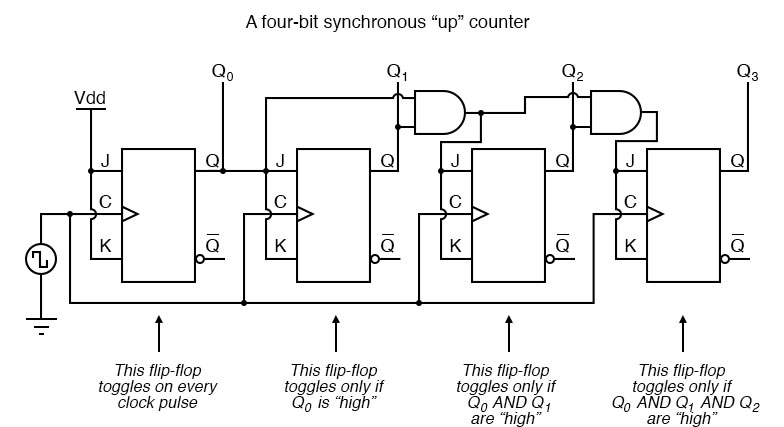

Solved Fig 6 12 4 Bit Synchronous Binary Counterthis Image Chegg A 4 bit decade synchronous counter can also be built using synchronous binary counters to produce a count sequence from 0 to 9. a standard binary counter can be converted to a decade (decimal 10) counter with the aid of some additional logic to implement the desired state sequence. A 4 bit synchronous counter using jk flip flops is an efficient and high speed counting circuit used in various digital applications. whether used as an up counter or down counter, it provides stable, glitch free counting.

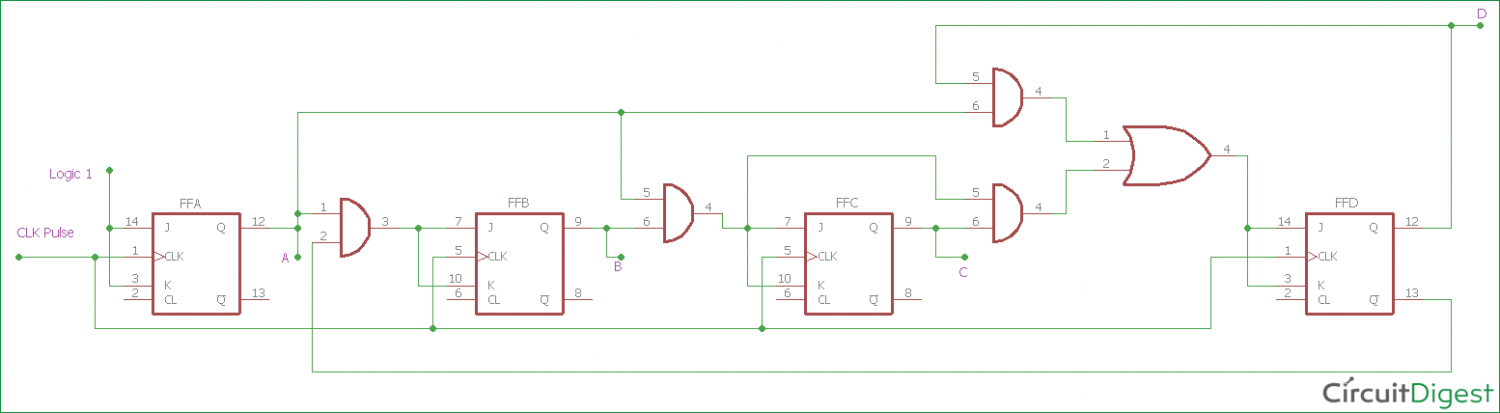

Circuit Diagram Of 4 Bit Synchronous Binary Counter The carry look ahead circuitry provides for cascading counters for n bit synchronous applications, without additional gating. this function is implemented by the enp and ent inputs and an rco output. This article explores the 4 bit binary counter working, circuit diagram, applications, how to design it using d or jk flip flop, and ic 74ls93, 7493, 74193. This document describes a 4 bit synchronous binary counter. it contains the truth table for a jk flip flop, diagrams of the counter circuit using 4 jk flip flops connected in series with a common clock, and tables showing the output logic states and timing diagram as the counter counts from 0 to 15 over 16 clock pulses. In this paper, we have presented a design of 4 bit binary synchronous counter using three different techniques namely cmos technique, sleepy transistor technique (stt) and forced stack.

Circuit Diagram Of 4 Bit Synchronous Binary Counter This document describes a 4 bit synchronous binary counter. it contains the truth table for a jk flip flop, diagrams of the counter circuit using 4 jk flip flops connected in series with a common clock, and tables showing the output logic states and timing diagram as the counter counts from 0 to 15 over 16 clock pulses. In this paper, we have presented a design of 4 bit binary synchronous counter using three different techniques namely cmos technique, sleepy transistor technique (stt) and forced stack. This document presents a project on designing a 4 bit binary synchronous up counter using electric software, focusing on the creation of a jk flip flop based counter that counts from 0000 to 1111. This system automatically counts from 0 to 15 in binary and displays the count on a set of four leds. this scenario is practical and ideal for beginners because it allows students to analyze the core concepts of sequential circuits, registers, and counters in a visual and tangible way. A counter is a digital electronic device that counts the number of times an event occurs using a clock signal. with each clock pulse, the count changes, such as in an up counter where the count increases by one. counters are built using flip flops and can follow fixed or custom sequences like 0, 1, 3, 2. they can also act as frequency dividers by reducing the input clock frequency. counters. In this paper, we have designed a 4 bit binary synchronous counter using cct, stt and fst. the circuit designing and parametric analysis has been carried out using microwind 3.1 and dsch 3.1 designing tools.

Comments are closed.