Effective Nonblocking Cache Architecture For Highperformance Texture

Prefetching In A Texture Cache Architecture Pdf Our approach improving texture cache performance improving cache hit rates reducing miss penalty reducing cache access time “our approach” in this presentation, we introduce a non blocking texture cache (nbtc) architecture out of order (ooo) execution conditional in order (io) completion the same screen coordinate to support the standard. Our approach • improving texture cache performance • improving cache hit rates • reducing miss penalty • reducing cache access time • in this presentation, we introduce a non blocking texture cache (nbtc) architecture • out of order (ooo) execution • conditional in order (io) completion • the same screen coordinate to support.

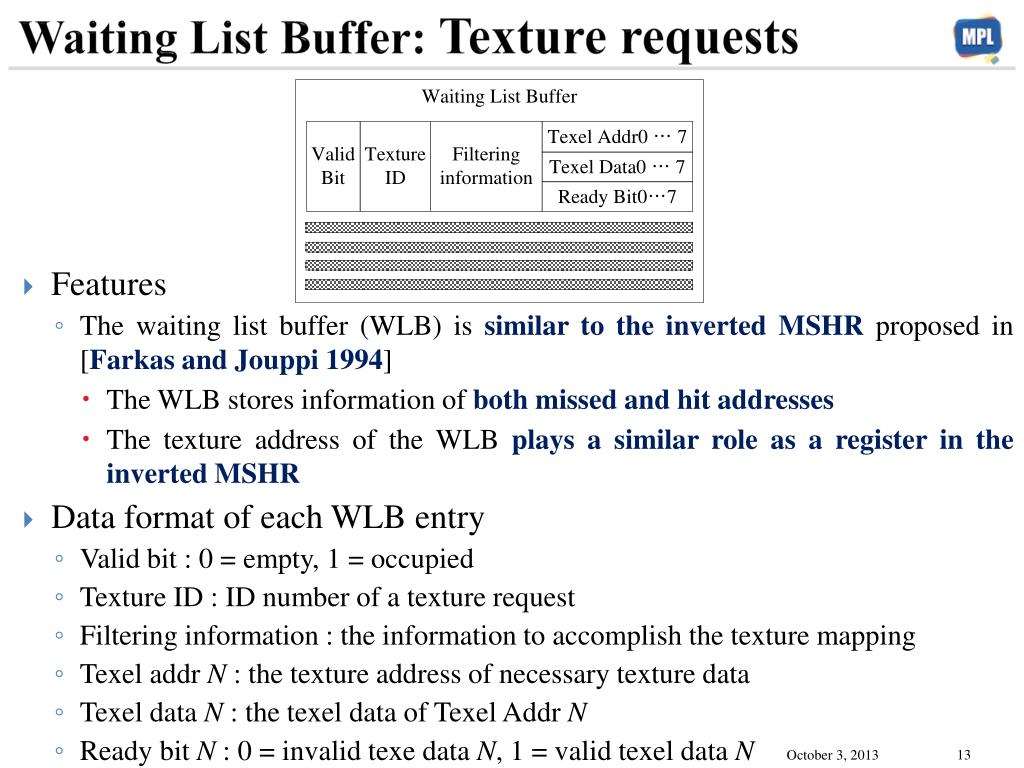

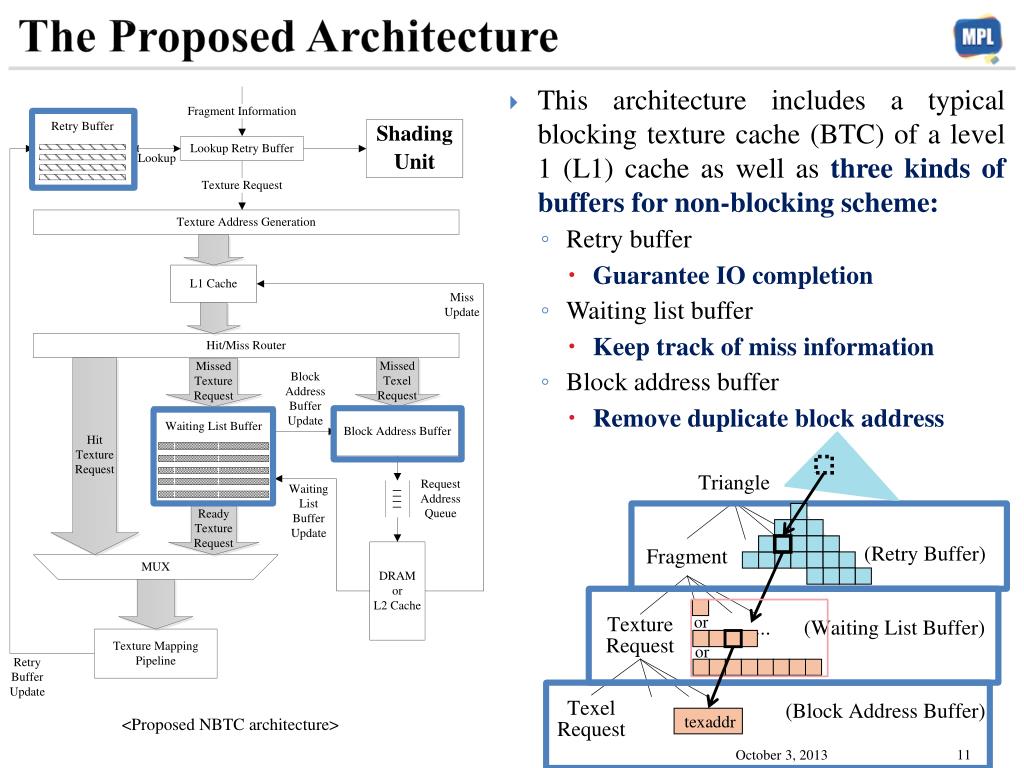

Effective Nonblocking Cache Architecture For Highperformance Texture Block request address queue address feature the block address buffer operates the dram access sequentially with regard to the texel request that caused a cache miss the block address buffer removes duplicate dram requests when data are loaded, all the removed dram requests are found the block address buffer is designed as fifo october 3, 2013. Block request address queue address feature the block address buffer operates the dram access sequentially with regard to the texel request that caused a cache miss the block address buffer removes duplicate dram requests when data are loaded, all the removed dram requests are found the block address buffer is designed as fifo october 3, 2013. In this work, we build an analytical model of the router and identify that cs is the actual bottleneck. then, we propose a novel mechanism called “nb cache” to address cs’s performance issue from a network wide point of view. In this paper, we introduce a texture architecture which com bines prefetching and caching. our architecture is designed to take advantage of the peculiar access characteristics of texture mapping.

Effective Nonblocking Cache Architecture For Highperformance Texture In this work, we build an analytical model of the router and identify that cs is the actual bottleneck. then, we propose a novel mechanism called “nb cache” to address cs’s performance issue from a network wide point of view. In this paper, we introduce a texture architecture which com bines prefetching and caching. our architecture is designed to take advantage of the peculiar access characteristics of texture mapping. Ient cache architecture for portable graphics devices. in partic ular, we propose a cache architecture for texture mapping, which is one of the most expensive tasks (both in terms of processing power as well as memory bandwidth). In this work, we build an analytical model of the router and identify that cs is the actual bottleneck. then, we propose a novel mechanism called “nb cache” to address cs’s performance issue from a network wide point of view. A non blocking cache for texture mapping is implemented by separating cache tags from cache data. multiple requests for data may be processed in parallel without strict ordering or. We present a new software texture caching algorithm that optimizes the use of texture memory in current graphics hardware by dynamically allocating more memory to the textures that have the greatest visual importance in the scene.

Ppt Effective Non Blocking Cache Architecture For High Performance Ient cache architecture for portable graphics devices. in partic ular, we propose a cache architecture for texture mapping, which is one of the most expensive tasks (both in terms of processing power as well as memory bandwidth). In this work, we build an analytical model of the router and identify that cs is the actual bottleneck. then, we propose a novel mechanism called “nb cache” to address cs’s performance issue from a network wide point of view. A non blocking cache for texture mapping is implemented by separating cache tags from cache data. multiple requests for data may be processed in parallel without strict ordering or. We present a new software texture caching algorithm that optimizes the use of texture memory in current graphics hardware by dynamically allocating more memory to the textures that have the greatest visual importance in the scene.

Ppt Effective Non Blocking Cache Architecture For High Performance A non blocking cache for texture mapping is implemented by separating cache tags from cache data. multiple requests for data may be processed in parallel without strict ordering or. We present a new software texture caching algorithm that optimizes the use of texture memory in current graphics hardware by dynamically allocating more memory to the textures that have the greatest visual importance in the scene.

Ppt Effective Non Blocking Cache Architecture For High Performance

Comments are closed.