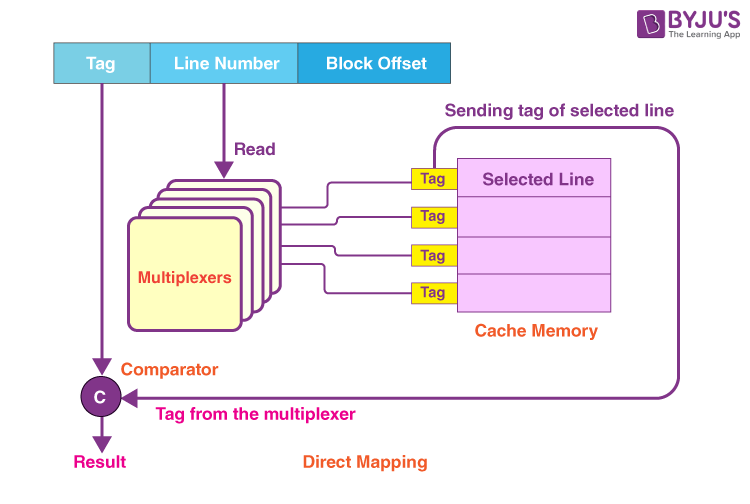

Direct Mapping Hardware Implementation

Direct Mapping Technique Download Free Pdf Cpu Cache Computer In direct mapping, each block of main memory maps to exactly one specific cache line. the main memory address is divided into three parts: tag bits: identify which block of memory is stored. line number: indicates which cache line it belongs to. byte offset: specifies the exact byte within the block. the formula for finding the cache line is: 2. Generally, an algorithm can be mapped to a software–hardware architecture either by direct mapping or by first mapping the algorithm to an intermediate, virtual machine followed by mapping to a programmable hardware structure.

Direct Memory Mapping Hardware Implementation Video Lecture Crash This approach offers a middle ground between direct and fully associative caches, reducing the likelihood of conflicts compared to direct mapping while avoiding the high hardware complexity of fully associative caches. In this article, i will try to explain the cache mapping techniques using their hardware implementation. this will help you visualize the difference between different mapping techniques, using which you can take informed decisions on which technique to use given your requirements. Direct memory mapping – hardware implementation explores the hardware structure of direct mapped caches, explaining hit latency, practical calculation examples, and architectural. A comprehensive configuration guide and code repository for the hw 364a and hw 364b esp8266 modules featuring integrated 0.96 inch oled displays. it provides corrected i2c pin mappings, implementation examples using the u8g2 library, and specific arduino ide configuration settings to ensure reliable operation.

Direct Mapping Direct memory mapping – hardware implementation explores the hardware structure of direct mapped caches, explaining hit latency, practical calculation examples, and architectural. A comprehensive configuration guide and code repository for the hw 364a and hw 364b esp8266 modules featuring integrated 0.96 inch oled displays. it provides corrected i2c pin mappings, implementation examples using the u8g2 library, and specific arduino ide configuration settings to ensure reliable operation. Direct mapping is simple and efficient but suffers from high conflict misses. associative mapping is flexible and minimizes conflict misses but is expensive and complex. Simple direct mapped cache simulation on fpga the subject of this article is the topic of the project for first year bachelors, the purpose of which is to show an understanding of the topic, or to help to understand it using simulation. This lecture provides a comprehensive, step‑by‑step examination of how a direct‑mapped cache services read and write requests, differentiates hits from misses, and preserves data correctness. Your assignment is to simulate a 4k direct mapping cache using c. the memory of this system is divided into 8 word blocks, which means that the 4k cache has 4k 8 = 512 lines.

Mapping The Gpu Implementation Into Hardware A Direct Map From The Direct mapping is simple and efficient but suffers from high conflict misses. associative mapping is flexible and minimizes conflict misses but is expensive and complex. Simple direct mapped cache simulation on fpga the subject of this article is the topic of the project for first year bachelors, the purpose of which is to show an understanding of the topic, or to help to understand it using simulation. This lecture provides a comprehensive, step‑by‑step examination of how a direct‑mapped cache services read and write requests, differentiates hits from misses, and preserves data correctness. Your assignment is to simulate a 4k direct mapping cache using c. the memory of this system is divided into 8 word blocks, which means that the 4k cache has 4k 8 = 512 lines.

Direct Mapping Gate Notes This lecture provides a comprehensive, step‑by‑step examination of how a direct‑mapped cache services read and write requests, differentiates hits from misses, and preserves data correctness. Your assignment is to simulate a 4k direct mapping cache using c. the memory of this system is divided into 8 word blocks, which means that the 4k cache has 4k 8 = 512 lines.

Direct Mapping Gate Notes

Comments are closed.