Computer Architecture Hw 5 6 Solution Arabic

Github Arsenijpercov Computer Architecture And Programming Languages This video answers the homework questions related the computer architecture lectures in facebook group. . finally your feedback is most welcome !!!. Memory hierarchy main memory memory management hardware objectives of chapter 5 by the end of this chapter, the student will be able to: decode the memory address and use the outputs of the decoder to select various memory components.

Solution Arabic Hw Nov Studypool Contribute to rasadell09 cs570 development by creating an account on github. Hi, welcome back! أو التسجيل باستخدام حسابك في جوجل (اضغط علي ايقونة جوجل) forgot password? don't have an account? register now. The document outlines problems related to cache memory, including calculations for cache block size, tag and index bits, and average memory access time (amat) for different configurations. it presents various scenarios with hit miss rates and compares performance metrics between two processors. Solutions manual for computer architecture textbook. includes solutions for chapters 1 6 and appendices a c. ideal for college students.

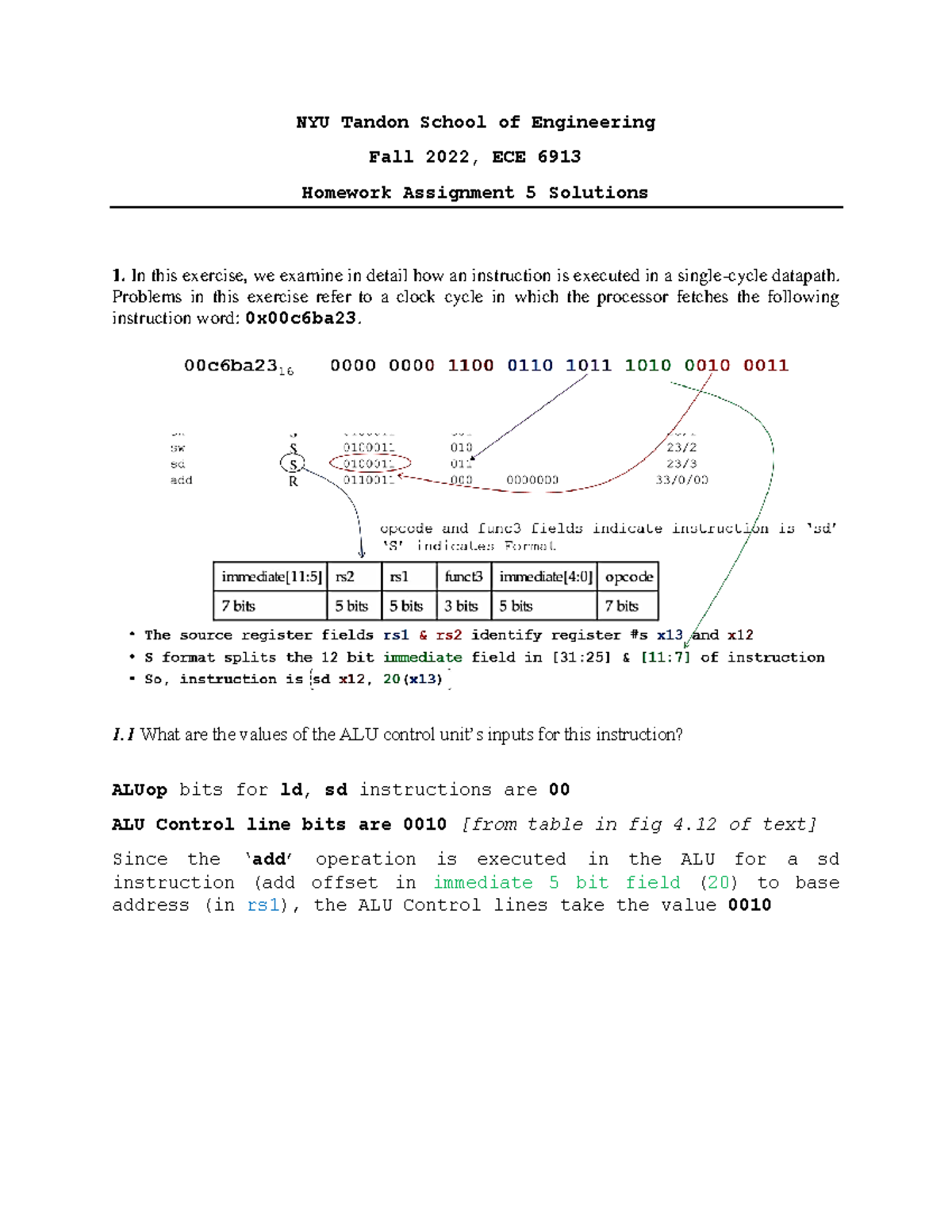

Hw 5 Ece 6913 Sol Hw Solutions Nyu Tandon School Of Engineering The document outlines problems related to cache memory, including calculations for cache block size, tag and index bits, and average memory access time (amat) for different configurations. it presents various scenarios with hit miss rates and compares performance metrics between two processors. Solutions manual for computer architecture textbook. includes solutions for chapters 1 6 and appendices a c. ideal for college students. 3 cores are needed to take the maximum advantage of each cache hit, and a maximum speed up of almost 3 can be achieved. core 1 calculates iterations i 0, i 1, i 2, i 3, core 2 calculates iteration i 4, i 5, i 6, i 7, and core 3 calculates iteration i 8, i 9, i 10, i 11. Homework #5 solutions computer architecture and design | elec 5200, assignments for computer architecture and organization. We wish to compare the performance of two different computers: m1 and m2. the following measurements have been made on these computers: (i) which computer is faster for each program, and how many times as fast is it? (ii) find the instruction execution rate (instructions per second) for each computer when running program 1. Remove the inverter from the e input in fig. 2.2(a). if all inputs equal 0 or if only d0 = 1: the outputs a2a1a0 = 000. needs one more output to recognize the all zeros input condition.

Comments are closed.