Complete Experimental Layout A Single Eac B Eac Device With Stack

Complete Experimental Layout A Single Eac B Eac Device With Stack In this work, the efforts to reduce nox emission by developing electrochemically activated cells (eacs) for a diesel engine fuelled with diesel and biodiesel fuel are discussed. In this work, the efforts to reduce nox emission by developing electrochemically activated cells (eacs) for a diesel engine fuelled with diesel and biodiesel fuel are discussed.

Complete Experimental Layout A Single Eac B Eac Device With Stack The bi polar and mono polar configurations of electrolysis stack have been fabricated by using the electrolysis cell, which has been developed in experiment viii, and the rest of the experiments have been implemented to investigate the performance of fabricated electrolysis stacks. In order to design a high performing and durable soe stack or system, all the relevant length scales should be addressed using different approaches and tools, and all the components of the balance of plant need to be properly dimensioned and integrated. Let’s take a look at a few ways of achieving a high quality layout for stacked mosfets. the subcircuit below shows four nmos mosfets that have been stacked together to create a long channel device. In this emc design guideline we concentrate on the rules, examples, simulations, and measurements for printed circuit board (pcb) layout. by using these rules it is possible to prevent high electromagnetic emission through a well designed pcb.

Eac Be Invisible Device Eac Be Https Monopol Gg Let’s take a look at a few ways of achieving a high quality layout for stacked mosfets. the subcircuit below shows four nmos mosfets that have been stacked together to create a long channel device. In this emc design guideline we concentrate on the rules, examples, simulations, and measurements for printed circuit board (pcb) layout. by using these rules it is possible to prevent high electromagnetic emission through a well designed pcb. A pcb stack up refers to the arrangement and sequence of copper foil, core materials, and prepreg (pre impregnated material) in a multilayer printed circuit board. it is far more than just “stacking layers”; it is a complete electrical, mechanical, and thermal management system. Design (mask set) foundry house (fab) design rules (layout) process parameters (simulation) we don’t care about the real details of the fab, but we have to define the patterning of the layers (that meet their rules) to specify our design. \stick" diagram and simpli ed layout of nand gate stick diagrams identify actual layers (which a schematic does not); both can be annotated with transistor sizes n and p wells are shown. An embedded array capacitor (eac) is a large array capacitor embedded in the high density interconnect (hdi) substrate core and provides a low inductance path to the die. this paper describes technology development challenges encoun tered while enabling eacs on intel’s advanced microprocessors.

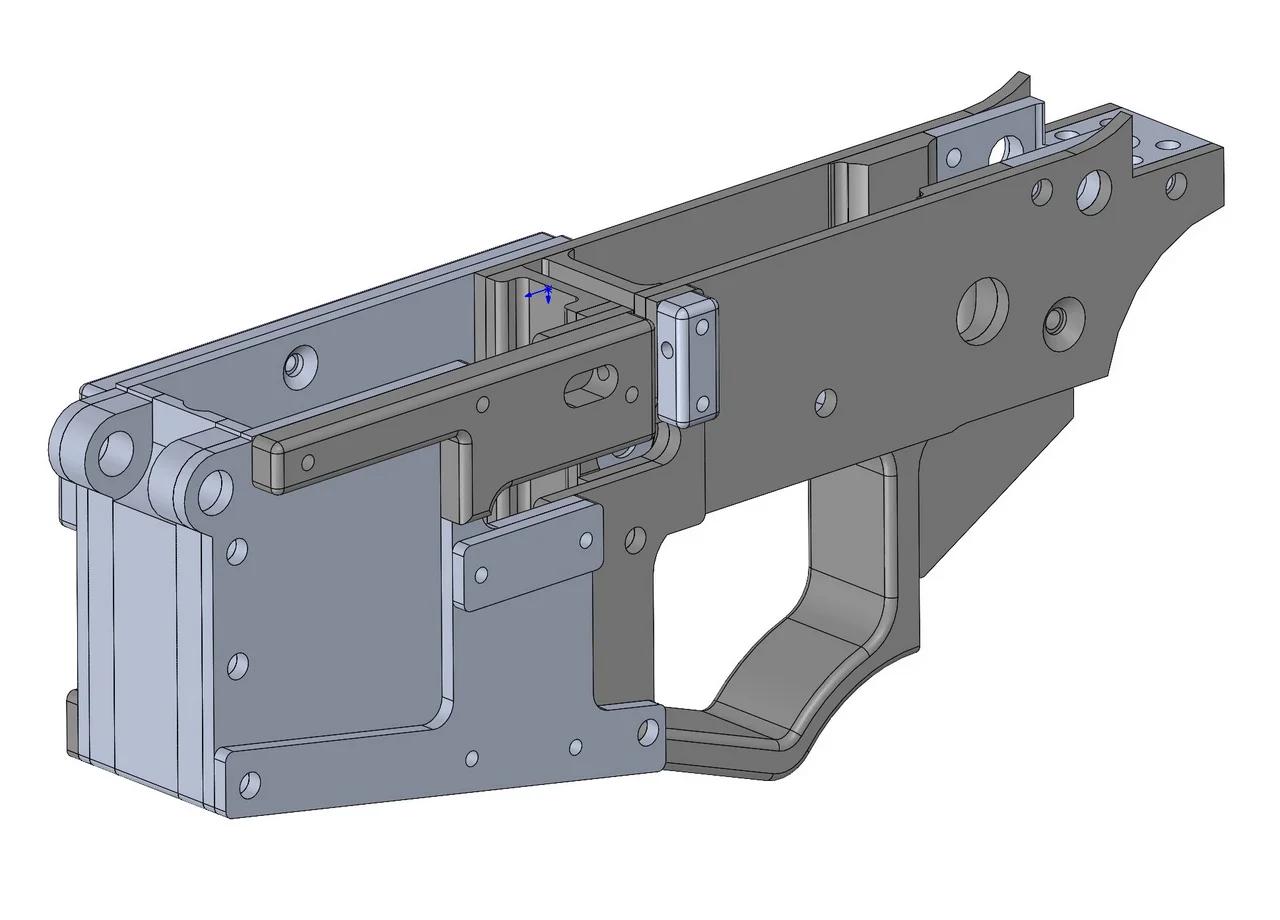

Plate Stack Receiver V3b Updates After Assembly A pcb stack up refers to the arrangement and sequence of copper foil, core materials, and prepreg (pre impregnated material) in a multilayer printed circuit board. it is far more than just “stacking layers”; it is a complete electrical, mechanical, and thermal management system. Design (mask set) foundry house (fab) design rules (layout) process parameters (simulation) we don’t care about the real details of the fab, but we have to define the patterning of the layers (that meet their rules) to specify our design. \stick" diagram and simpli ed layout of nand gate stick diagrams identify actual layers (which a schematic does not); both can be annotated with transistor sizes n and p wells are shown. An embedded array capacitor (eac) is a large array capacitor embedded in the high density interconnect (hdi) substrate core and provides a low inductance path to the die. this paper describes technology development challenges encoun tered while enabling eacs on intel’s advanced microprocessors.

Schematic Layout Of Experimental Device Download Scientific Diagram \stick" diagram and simpli ed layout of nand gate stick diagrams identify actual layers (which a schematic does not); both can be annotated with transistor sizes n and p wells are shown. An embedded array capacitor (eac) is a large array capacitor embedded in the high density interconnect (hdi) substrate core and provides a low inductance path to the die. this paper describes technology development challenges encoun tered while enabling eacs on intel’s advanced microprocessors.

Results Of Micro Ct Analysis A 3d Reconstruction B Bulk Eac Device C

Comments are closed.