Cmp Lapping Silicon Wafer In Semiconductor Industry

Semiconductor Wafer Lapping And Displacement Measurement Vitrek Educational guide to wafer polishing and lapping best practices, including cmp fundamentals, abrasive selection, scratch removal progression, surface roughness targets, flatness ttv control, and material specific tips for silicon, sic, sapphire, and advanced semiconductor wafers. Grinding and lapping are two widely used machining processes for silicon wafer planarization. their resultant surface integrity has a significant impact on subsequent polishing and hence the overall manufacturing cost.

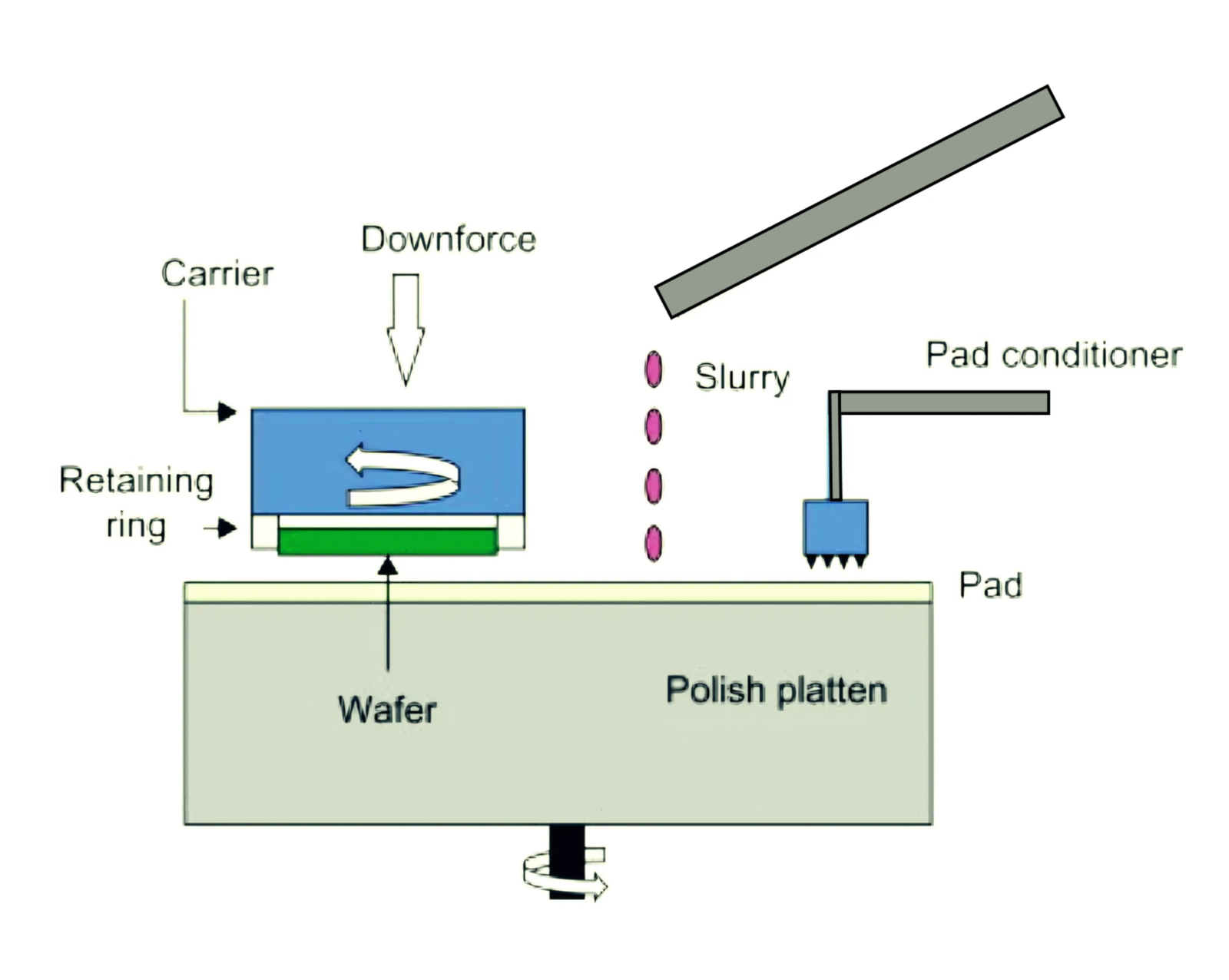

Semiconductor Wafer Lapping And Displacement Measurement Vitrek Chemical mechanical polishing (cmp) technology is currently considered to be the only process that can achieve overall flatness of large size silicon wafers, and the polishing accuracy directly determines the surface quality and performance of silicon wafers. Objective: achieve single side lapping and chemical mechanical polishing (cmp) of a 4” diameter silicon wafer to a final thickness of 500 µm, with a target surface finish (ra) of 1–2 nm. Fabrication of commercial integrated circuits depends critically on the physical and chemical properties of the abrasive slurry particles used to polish silicon wafer surfaces via chemical mechanical planarization (cmp) to near atomic flatness. Wafers are then chemically mechanically polished planarized (cmp) for the final material removal stage, to attain a super flat mirror like surface with a remaining roughness on an atomic scale. the wafer is then ready for device fabrication.

Semiconductor Fabrication From Silicon Wafer To Microchip Fabrication of commercial integrated circuits depends critically on the physical and chemical properties of the abrasive slurry particles used to polish silicon wafer surfaces via chemical mechanical planarization (cmp) to near atomic flatness. Wafers are then chemically mechanically polished planarized (cmp) for the final material removal stage, to attain a super flat mirror like surface with a remaining roughness on an atomic scale. the wafer is then ready for device fabrication. What is wafer polishing? wafer polishing, also known as chemical mechanical polishing (cmp), is a process used to smooth and flatten the surface of semiconductor wafers. this step is essential in the fabrication of integrated circuits (ics) and other semiconductor devices. Lapping and polishing are critical: they require time consuming steps and strict control of wafer total thickness variation. thanks to the marposs infrared sensor, it is possible to control the thickness during and immediately after this crucial operation. The wafer polishing process, also known as chemical mechanical planarization (cmp), is a critical step in semiconductor manufacturing, ensuring silicon wafers achieve the necessary surface smoothness, flatness, and defect free characteristics required for high performance electronic devices. In order to compensate for the wafer bow, pressure can be applied to the wafer's backside which, in turn, will equalize the centre edge differences. the pads used in the cmp tool should be rigid in order to uniformly polish the wafer surface.

Premium Photo Silicon Wafer For Manufacturing Semiconductor Of What is wafer polishing? wafer polishing, also known as chemical mechanical polishing (cmp), is a process used to smooth and flatten the surface of semiconductor wafers. this step is essential in the fabrication of integrated circuits (ics) and other semiconductor devices. Lapping and polishing are critical: they require time consuming steps and strict control of wafer total thickness variation. thanks to the marposs infrared sensor, it is possible to control the thickness during and immediately after this crucial operation. The wafer polishing process, also known as chemical mechanical planarization (cmp), is a critical step in semiconductor manufacturing, ensuring silicon wafers achieve the necessary surface smoothness, flatness, and defect free characteristics required for high performance electronic devices. In order to compensate for the wafer bow, pressure can be applied to the wafer's backside which, in turn, will equalize the centre edge differences. the pads used in the cmp tool should be rigid in order to uniformly polish the wafer surface.

Photograph Of Silicon Wafer After Grinding And Cmp A Silicon Wafer The wafer polishing process, also known as chemical mechanical planarization (cmp), is a critical step in semiconductor manufacturing, ensuring silicon wafers achieve the necessary surface smoothness, flatness, and defect free characteristics required for high performance electronic devices. In order to compensate for the wafer bow, pressure can be applied to the wafer's backside which, in turn, will equalize the centre edge differences. the pads used in the cmp tool should be rigid in order to uniformly polish the wafer surface.

Comments are closed.