Clock Domain Crossing Cdc

Machine Learning Cdc Clock Domain Crossing Real Intent Clock domain crossing is one of the first few topics that any interviewer will ask you about once the basics are out of the way. this article aims to be a quick reference guide and an exhaustive checklist for designers to keep coming back to. In digital electronic design a clock domain crossing (cdc), or simply clock crossing, is the traversal of a signal in a synchronous digital circuit from one clock domain into another.

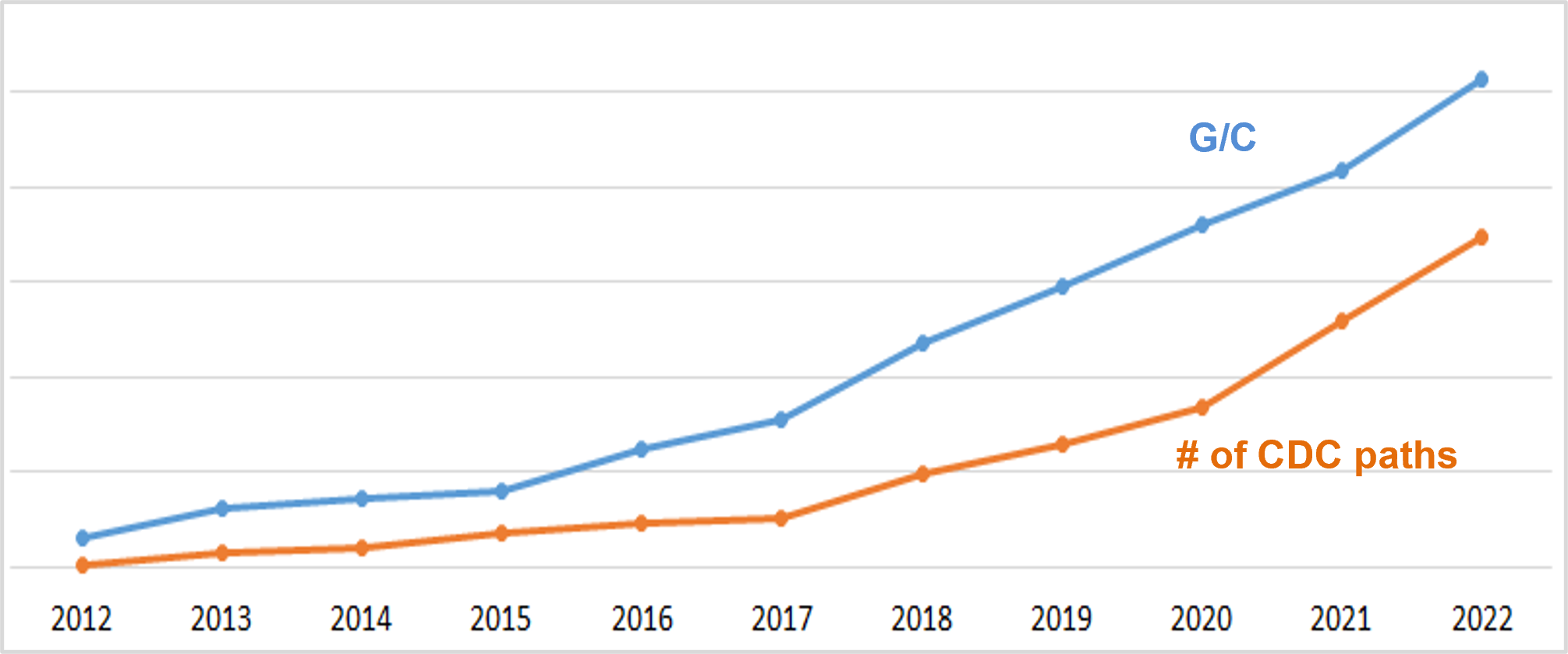

Vlsi Asic Physical Design Concepts Clock Domain Crossing Cdc What is clock domain crossing (cdc)? formally clock domain crossing (cdc) in digital domain is defined as: “the process of passing a signal or vector (multi bit signal) from one clock domain to another clock domain.”. Clock domain is all of the sequential logic that runs on the same clock clock frequency may have multiple clock domains in one device or different clock domains when communicating across devices. Modern digital systems frequently rely on multiple clock domains to meet performance, power, and modularity requirements. as soon as signals cross between these domains, designers face one of the most subtle and error prone challenges in rtl design: clock domain crossing (cdc). Clock domain crossing (cdc) is a significant challenge in digital design, keeping design and verification engineers vigilant. it occurs when different parts of a digital system, each operating under distinct clock domains, need to communicate with one another.

Vlsi Asic Physical Design Concepts Clock Domain Crossing Cdc Modern digital systems frequently rely on multiple clock domains to meet performance, power, and modularity requirements. as soon as signals cross between these domains, designers face one of the most subtle and error prone challenges in rtl design: clock domain crossing (cdc). Clock domain crossing (cdc) is a significant challenge in digital design, keeping design and verification engineers vigilant. it occurs when different parts of a digital system, each operating under distinct clock domains, need to communicate with one another. Clock domain crossing (cdc) refers to the process of transferring data between two different clock domains in a digital system. it’s a critical design challenge because differences in clock timing can cause data corruption or synchronization issues if not handled properly. Attributes for a block that can be used to facilitate a correct clock domain crossing and reset domain crossing integration of that block in an encompassing design are identified. Discover the essentials of clock domain crossing (cdc) and learn why it’s critical for reliable digital design. understand metastability, synchronization, and best practices for handling cdc. Cdc occurs when a signal is transmitted from a flip flop in one clock domain to a flip flop in another clock domain. the two clock domains may be asynchronous, meaning their clocks are not synchronized, or they may have different frequencies or phases.

Comments are closed.