Chipmonc Logic Diagrams

Logic Diagrams Technical Training Professionals Ttp Grasp the concepts of rtl design, start designing your own chips in verilog vhdl. free open source codes of ip cores to use in your designs, insightful blogs. It enables timing analysis (sta) of the. design and helps to understand how good the design is timing performance wise. and discusses how to write the sdc timing constraints for the clocks. timing exceptions are also. discussed with examples. tool specific options are also discussed in some examples. the.

Logic Diagrams General Topics The Lounge Mrplc In this instructable, we are going to design a simple vga controller in rtl. vga controller is the digital circuit designed to drive vga displays. it reads from frame buffer (vga memory) which represents the frame to be displayed, and generates necessary data and sync signals for display purpose. Written by john lazzaro and david gillespie at caltech in the 1980s, and maintained and updated upgraded through the early 1990s, the circuit simulation programs analog and diglog together comprise one of the best circuit simulation software tools ever written. In this webinar, matthew taylor, senior member of technical staff at doulos, will: 1 demonstrate what pss can achieve using a simple uvm example. 2 explain the core features and syntax of the pss. We all worked together to develop the design and functionality for chipmonc. we discussed instruction format, types of instructions to execute, and the basic ideas of how to implement the circuit.

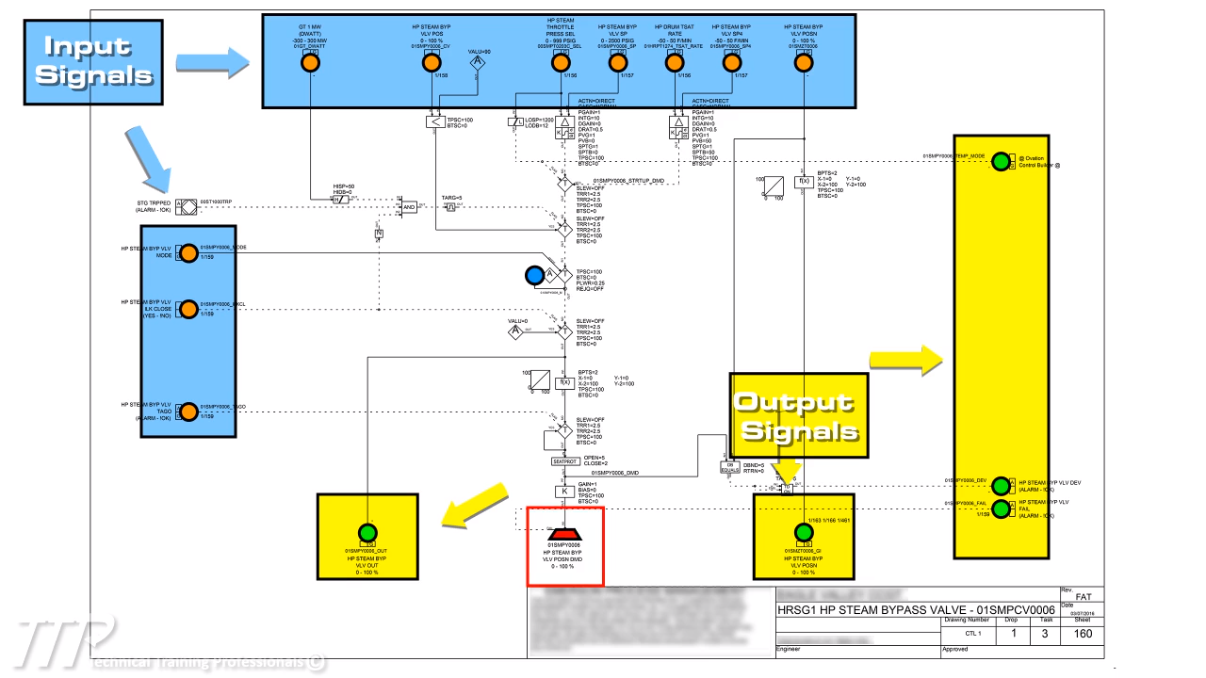

Design Logic Diagrams With Standard Formats For Process Control In this webinar, matthew taylor, senior member of technical staff at doulos, will: 1 demonstrate what pss can achieve using a simple uvm example. 2 explain the core features and syntax of the pss. We all worked together to develop the design and functionality for chipmonc. we discussed instruction format, types of instructions to execute, and the basic ideas of how to implement the circuit. 👔 founder & ceo at chipmunk logic™ 👀 i’m into rtl design, embedded software development, gui cli software development for os, scripts, math, physics and much more. In this blog, we define the full specs and architecture of pequeno. last time, it was simply defined to be a 32 bit cpu. let us put more details into it to get the picture of architecture to be designed. Designing a synchronous fifo, lifo stack in verilog: this is to inform that this blog is now archived and i have started a new website blog of my own: chipmunk logic. Along with the rtl, i have always made it a habit to write the timing constraints for the designs whenever i compile and synthesise the rtl on fpgas. it enables timing analysis (sta) of the design and helps to understand how good the design is timing performance wise.

Digibarn Diagrams Original Macintosh 512k Logic Board Schematic 👔 founder & ceo at chipmunk logic™ 👀 i’m into rtl design, embedded software development, gui cli software development for os, scripts, math, physics and much more. In this blog, we define the full specs and architecture of pequeno. last time, it was simply defined to be a 32 bit cpu. let us put more details into it to get the picture of architecture to be designed. Designing a synchronous fifo, lifo stack in verilog: this is to inform that this blog is now archived and i have started a new website blog of my own: chipmunk logic. Along with the rtl, i have always made it a habit to write the timing constraints for the designs whenever i compile and synthesise the rtl on fpgas. it enables timing analysis (sta) of the design and helps to understand how good the design is timing performance wise.

Comments are closed.