Cache Controller Poster 1 Pdf Cpu Cache Cache Computing

Cpu Cache How Caching Works Pdf Cpu Cache Random Access Memory Cache controller poster (1) free download as pdf file (.pdf), text file (.txt) or read online for free. Cache controller for two level cache (direct mapped l1 cache and 4 way set associative l2 cache) with latencies and wait signal. policies used write back, write no allocate and least recently used policy.

Cache Org Pdf Cpu Cache Computing Answer: a n way set associative cache is like having n direct mapped caches in parallel. In order to maintain a coherent memory system, we now enhance our cache control unit to implement an msi cache coherency protocol. the msi protocol and updated ccu diagram are shown in the fig. 4 and fig. 5, respectively. How should space be allocated to threads in a shared cache? should we store data in compressed format in some caches? how do we do better reuse prediction & management in caches?. Cs 0019 21st february 2024 (lecture notes derived from material from phil gibbons, randy bryant, and dave o’hallaron) 1 ¢ cache memories are small, fast sram based memories managed automatically in hardware § hold frequently accessed blocks of main memory.

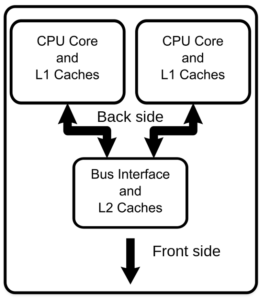

Cpu Cache Explained Twit Iq How should space be allocated to threads in a shared cache? should we store data in compressed format in some caches? how do we do better reuse prediction & management in caches?. Cs 0019 21st february 2024 (lecture notes derived from material from phil gibbons, randy bryant, and dave o’hallaron) 1 ¢ cache memories are small, fast sram based memories managed automatically in hardware § hold frequently accessed blocks of main memory. Memory tradeoff fastest memory is on same chip as cpu but it is not very big (say, 32 kb in l1 cache) slowest memory is dram on different chips but can be very large (say, 256gb in compute server) goal: illusion that large memory is fast idea: use small memory as cache for large memory. Ect 1: cache controller – secondary component specifications the cache controller must interact with two other components: a cpu, which generates memory access requests, and. a main memory controller which manages the system main memory. this docum. cribes in detail the interfaces of these two components. cpu the cpu generates either read or wr. In computer architecture, almost everything is a cache! branch target bufer a cache on branch targets. most processors today have three levels of caches. one major design constraint for caches is their physical sizes on cpu die. limited by their sizes, we cannot have too many caches. In this project you will use verilog to implement a data cache and its controller for a single cycle processor implementation.

Cpu Cache Basics Dev Community Memory tradeoff fastest memory is on same chip as cpu but it is not very big (say, 32 kb in l1 cache) slowest memory is dram on different chips but can be very large (say, 256gb in compute server) goal: illusion that large memory is fast idea: use small memory as cache for large memory. Ect 1: cache controller – secondary component specifications the cache controller must interact with two other components: a cpu, which generates memory access requests, and. a main memory controller which manages the system main memory. this docum. cribes in detail the interfaces of these two components. cpu the cpu generates either read or wr. In computer architecture, almost everything is a cache! branch target bufer a cache on branch targets. most processors today have three levels of caches. one major design constraint for caches is their physical sizes on cpu die. limited by their sizes, we cannot have too many caches. In this project you will use verilog to implement a data cache and its controller for a single cycle processor implementation.

Design Of Cache Controller Vlsi Excellence In computer architecture, almost everything is a cache! branch target bufer a cache on branch targets. most processors today have three levels of caches. one major design constraint for caches is their physical sizes on cpu die. limited by their sizes, we cannot have too many caches. In this project you will use verilog to implement a data cache and its controller for a single cycle processor implementation.

Cache Controller Poster 1 Pdf Cpu Cache Cache Computing

Comments are closed.