Binary To Bcd Verilog Project

Binary 2 Bcd Project Pdf Binary Coded Decimal Bit This project implements three verilog modules to perform conversions between binary and bcd (binary coded decimal): binary to bcd converter – uses the efficient double dabble algorithm (shift and add 3). Written in verilog, with parameters for the input and output widths, these simple cores illustrate the use of functions in verilog for performing operations that are not easy to do any other way in a fully parameterized (scalable) block of logic.

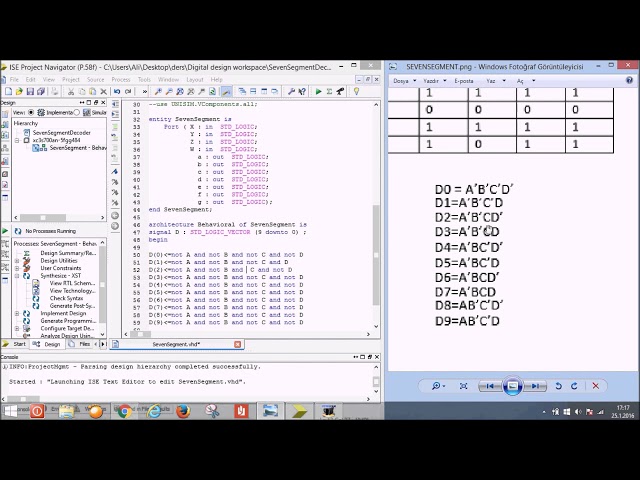

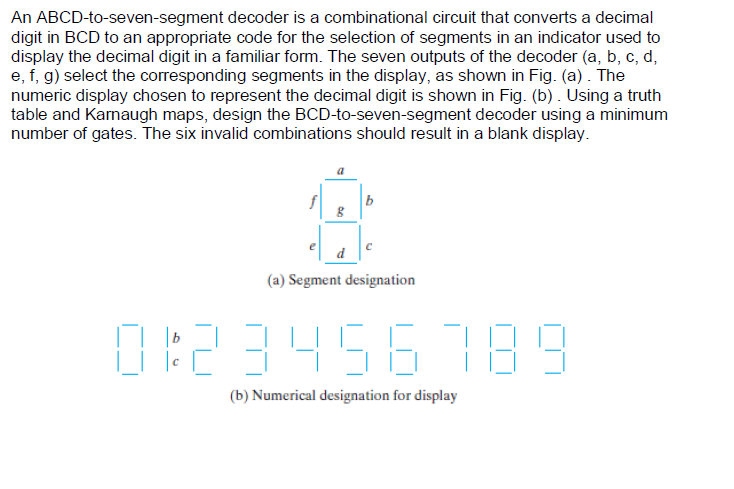

Binary To Bcd Converter Pdf Binary 2 bcd project free download as pdf file (.pdf), text file (.txt) or read online for free. this document describes a project to implement a binary to bcd to 7 segment display converter in verilog. This module takes an input binary vector and converts it to binary coded decimal (bcd). binary coded decimal is used to represent a decimal number with four bits. For verilog, its standard is to support division and remainder operations, and the synthesizer will also have ip to perform division operations. but this will consume too much resources, and the conversion from binary to bcd code can be realized by using the shift plus 3 algorithm. The code uses internal variables to store the individual bcd digits and converts each digit from binary to bcd using case statements. finally, the bcd digits are combined into a 16 bit bcd representation. this verilog code can be used in digital design projects that require binary to bcd conversion.

Binary To Bcd Vhd Pdf Binary Coded Decimal Bit For verilog, its standard is to support division and remainder operations, and the synthesizer will also have ip to perform division operations. but this will consume too much resources, and the conversion from binary to bcd code can be realized by using the shift plus 3 algorithm. The code uses internal variables to store the individual bcd digits and converts each digit from binary to bcd using case statements. finally, the bcd digits are combined into a 16 bit bcd representation. this verilog code can be used in digital design projects that require binary to bcd conversion. Write a systemverilog code for a 4 bit binary to bcd (binary coded decimal) converter. sure, here’s an example of a 4 bit binary to bcd (binary coded decimal) converter implemented using systemverilog:. In this project, we design a binary to bcd converter module in verilog, implemented on an artix 7 fpga.the design takes a binary number as input and outputs its binary coded decimal (bcd). This design is based on high speed low power architecture for fixed bit binary to bcd conversion. the design tested using modelsim and xilinx ise software. you can download the verilog hdl code to execute the design. Binary to bcd converter in verilog 🔧 description: this project converts an 8 bit binary number (0–255) into its corresponding 3 digit bcd output (hundreds, tens, ones) using the double dabble algorithm.

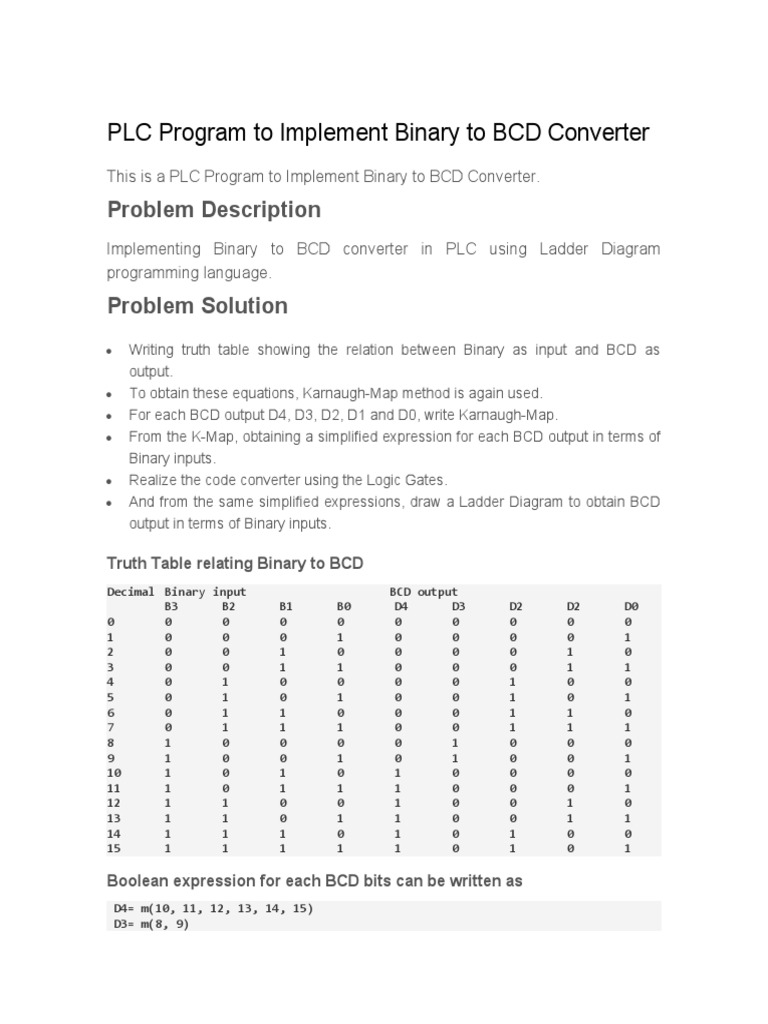

6 Plc Program To Implement Binary To Bcd Converter Pdf Binary Coded Write a systemverilog code for a 4 bit binary to bcd (binary coded decimal) converter. sure, here’s an example of a 4 bit binary to bcd (binary coded decimal) converter implemented using systemverilog:. In this project, we design a binary to bcd converter module in verilog, implemented on an artix 7 fpga.the design takes a binary number as input and outputs its binary coded decimal (bcd). This design is based on high speed low power architecture for fixed bit binary to bcd conversion. the design tested using modelsim and xilinx ise software. you can download the verilog hdl code to execute the design. Binary to bcd converter in verilog 🔧 description: this project converts an 8 bit binary number (0–255) into its corresponding 3 digit bcd output (hundreds, tens, ones) using the double dabble algorithm.

Verilog For Bcd To 7segment Display Verilog For Bcd To 41 Off This design is based on high speed low power architecture for fixed bit binary to bcd conversion. the design tested using modelsim and xilinx ise software. you can download the verilog hdl code to execute the design. Binary to bcd converter in verilog 🔧 description: this project converts an 8 bit binary number (0–255) into its corresponding 3 digit bcd output (hundreds, tens, ones) using the double dabble algorithm.

Verilog For Bcd To 7segment Display Verilog For Bcd To 41 Off

Comments are closed.