Bcd Counter Lab Fpga Implementation Pdf Binary Coded Decimal

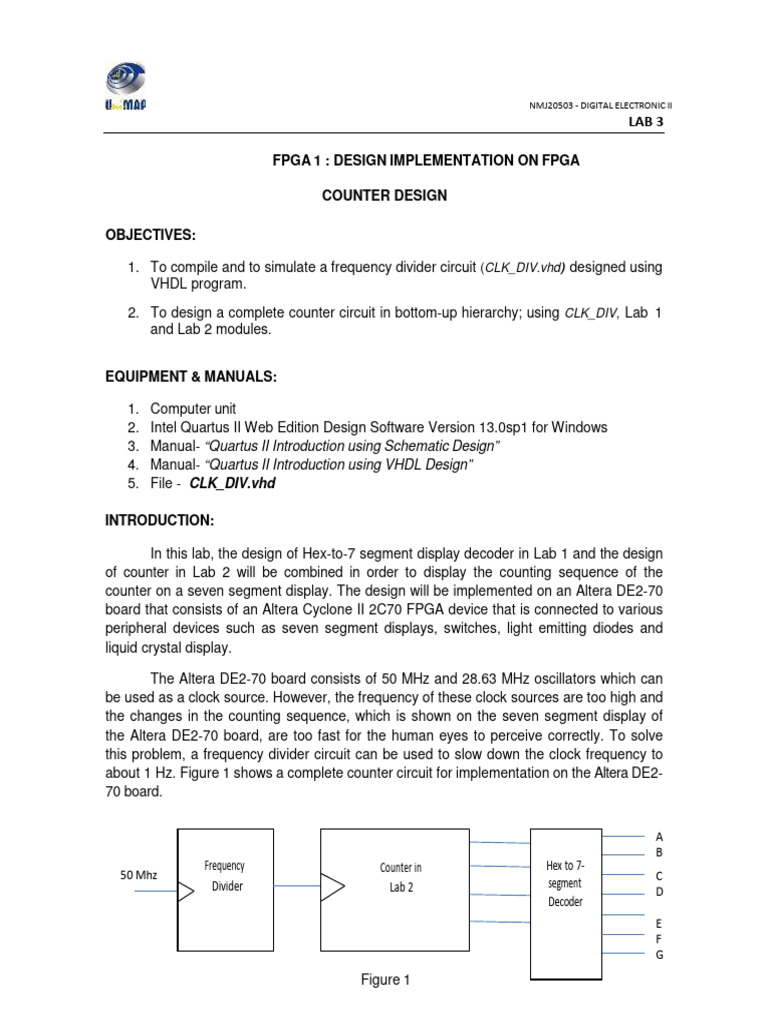

Lab 3 Fpga 1 Design Implementation On Fpga Counter Design V1 Pdf This lab aims to implement a 4 bit binary coded decimal (bcd) counter on an fpga board. students will write verilog code for a bcd counter module and a 7 segment decoder module. Parts: code the behavioral description of the 4 bit bcd counter. connect the bcd counter and the seven segment decoder.

Lab 5 4 Decimal To Bcd Encoder Pdf Binary Coded Decimal Logic Gate This project implements a binary coded decimal (bcd) counter using verilog and displays the count on a seven segment display. the counter increments from 0 to 9 on each clock pulse and wraps back to 0 after 9. the project runs on the terasic de10 standard fpga board. In this lab you will design a single digit bcd counter. a test module provided by the instructor will use four instances of your module to create a four digit up down counter whose digits will be dis played on the multiplexed led display used in the previous lab. So the table below lists the outputs that should be 1 for each decimal digit, under the assumption that all other segments should be 0, indicating a segment that is not lit. Explore the implementation of a bcd counter in fpga lab, focusing on design, simulation, and practical applications in digital electronics.

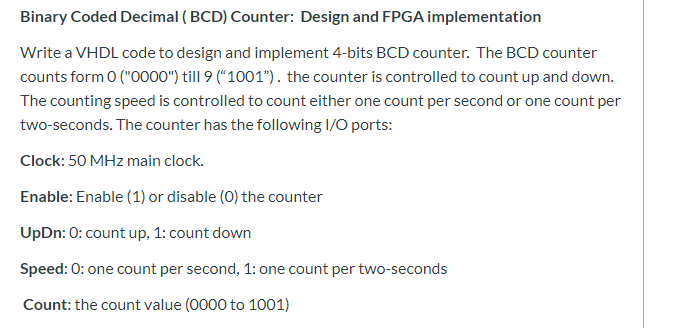

Solved Binary Coded Decimal Bcd Counter Design And Fpga Chegg So the table below lists the outputs that should be 1 for each decimal digit, under the assumption that all other segments should be 0, indicating a segment that is not lit. Explore the implementation of a bcd counter in fpga lab, focusing on design, simulation, and practical applications in digital electronics. Lab 19: building an 4 digit decimal down counter with 4 digit readout which starts at a user selected value. in this lab you will build upon your previous experience with the digilab board. Let’s not have an input to trigger each count, but instead let’s act as the clock by substituting a push button switch tied to the positive terminal of our power supply (which is equivalent to a logic 1). Design a combinational circuit that converts a 6 bit binary number into a 2 digit decimal number represented in the bcd form. use switches sw5 0 to input the binary number and 7 segment displays hex1 and hex0 to display the decimal number. This lab will have you build a simple 20 bit binary counter, and display in hexadecimal the counter output on the 7 segment leds. for this counter, you will understand how the synchronous clear and carry in input lines work.

Solved Binary Coded Decimal Bcd Counter Design And Fpga Chegg Lab 19: building an 4 digit decimal down counter with 4 digit readout which starts at a user selected value. in this lab you will build upon your previous experience with the digilab board. Let’s not have an input to trigger each count, but instead let’s act as the clock by substituting a push button switch tied to the positive terminal of our power supply (which is equivalent to a logic 1). Design a combinational circuit that converts a 6 bit binary number into a 2 digit decimal number represented in the bcd form. use switches sw5 0 to input the binary number and 7 segment displays hex1 and hex0 to display the decimal number. This lab will have you build a simple 20 bit binary counter, and display in hexadecimal the counter output on the 7 segment leds. for this counter, you will understand how the synchronous clear and carry in input lines work.

Comments are closed.