Basic Hdl Code Generation And Fpga Synthesis From Matlab Matlab

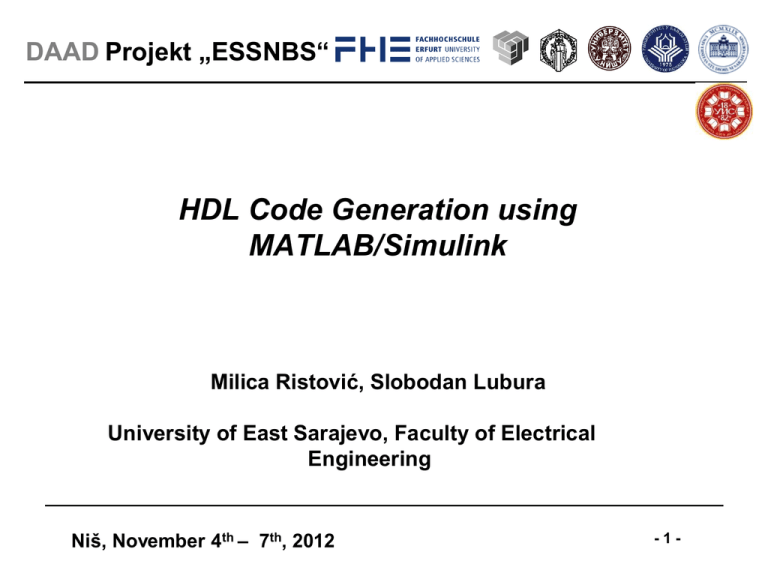

Ppt Hdl Code Generation Using Matlab Simulink Powerpoint Presentation This example shows how to create a hdl coder™ project, generate code for your matlab® design, and synthesize the hdl code. This design example presents matlab hdl coder, an add on that can generate vhdl and verilog code from matlab functions or simulink models.

Ppt Hdl Code Generation Using Matlab Simulink Powerpoint Presentation This tutorial will guide you through the steps necessary to implement a matlab algorithm in fpga hardware, including: learn how to deploy an algorithm to an fpga using matlab and simulink. It involves initializing the xilinx ise tools in matlab, creating a project, converting the matlab code to fixed point, generating hdl code from the fixed point matlab, and running synthesis and analysis in xilinx ise. Hdl coder enables high level design for fpgas, socs, and asics by generating portable, synthesizable verilog, systemverilog, and vhdl code from matlab functions, simulink models, and stateflow charts. The hdl coder app generates synthesizable hdl code and hls code from matlab ® code that is supported for hardware. you can generate vhdl, verilog, systemverilog, or hls code that you can integrate into existing hdl applications outside of matlab.

Hdl Code Generation With Matlab Simulink Hdl coder enables high level design for fpgas, socs, and asics by generating portable, synthesizable verilog, systemverilog, and vhdl code from matlab functions, simulink models, and stateflow charts. The hdl coder app generates synthesizable hdl code and hls code from matlab ® code that is supported for hardware. you can generate vhdl, verilog, systemverilog, or hls code that you can integrate into existing hdl applications outside of matlab. Follow the workflow for hdl code generation and fpga synthesis from matlab and simulink algorithms. Implement your matlab algorithm in hardware by generating hdl code and deploying that code on an application specific integrated circuit (asic) or field programmable gate array (fpga). Hdl coder enables high level design for fpgas, socs, and asics by generating portable, synthesizable verilog ®, systemverilog, and vhdl ® code from matlab functions, simulink models, and stateflow charts. This example shows how to use the hdl coder™ command line interface to generate hdl code from matlab® code, including floating point to fixed point conversion and fpga programming file generation.

Mathworks Matlab Now Supports Hdl Code Generation Ee Times Follow the workflow for hdl code generation and fpga synthesis from matlab and simulink algorithms. Implement your matlab algorithm in hardware by generating hdl code and deploying that code on an application specific integrated circuit (asic) or field programmable gate array (fpga). Hdl coder enables high level design for fpgas, socs, and asics by generating portable, synthesizable verilog ®, systemverilog, and vhdl ® code from matlab functions, simulink models, and stateflow charts. This example shows how to use the hdl coder™ command line interface to generate hdl code from matlab® code, including floating point to fixed point conversion and fpga programming file generation.

Mathworks Matlab Now Supports Hdl Code Generation Ee Times Hdl coder enables high level design for fpgas, socs, and asics by generating portable, synthesizable verilog ®, systemverilog, and vhdl ® code from matlab functions, simulink models, and stateflow charts. This example shows how to use the hdl coder™ command line interface to generate hdl code from matlab® code, including floating point to fixed point conversion and fpga programming file generation.

Comments are closed.