Assertions Happylearning Vlsiverification Asicdesign

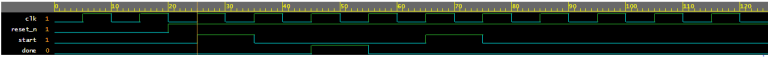

Built In Methods In Assertions Vlsi Worlds In this session, you’ll learn: 🔹 fundamentals of asic design & verification 🔹 role of systemverilog in functional verification 🔹 overview of testbenches, assertions, and coverage 🔹. Today, we will look at one example before ending this basic series on assertions. 👉 write the assertions for a simple t flipflop without and with reset. ♦ #t flip flop with no change property.

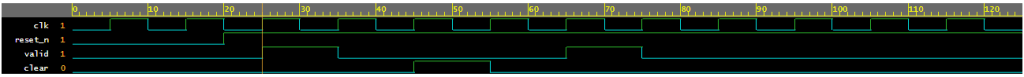

Built In Methods In Assertions Vlsi Worlds Assertions are powerful statements that automatically check your design's behavior during simulation. they catch bugs immediately when they happen, not hours later when you're debugging waveforms. this is your complete guide to mastering sva. A detailed explanation of assertions in vlsi, their types, and their role in verification. The verification plan includes a test plan (list of test cases that target design features), functional coverage planning, module block assignments to the verification engineers, checker, and assertion planning. Initially, at the level b, bugs can be caught using the directed testcase. however, once the bug count starts dropping, it’s time to introduce corner cases, functional coverage, and assertions.

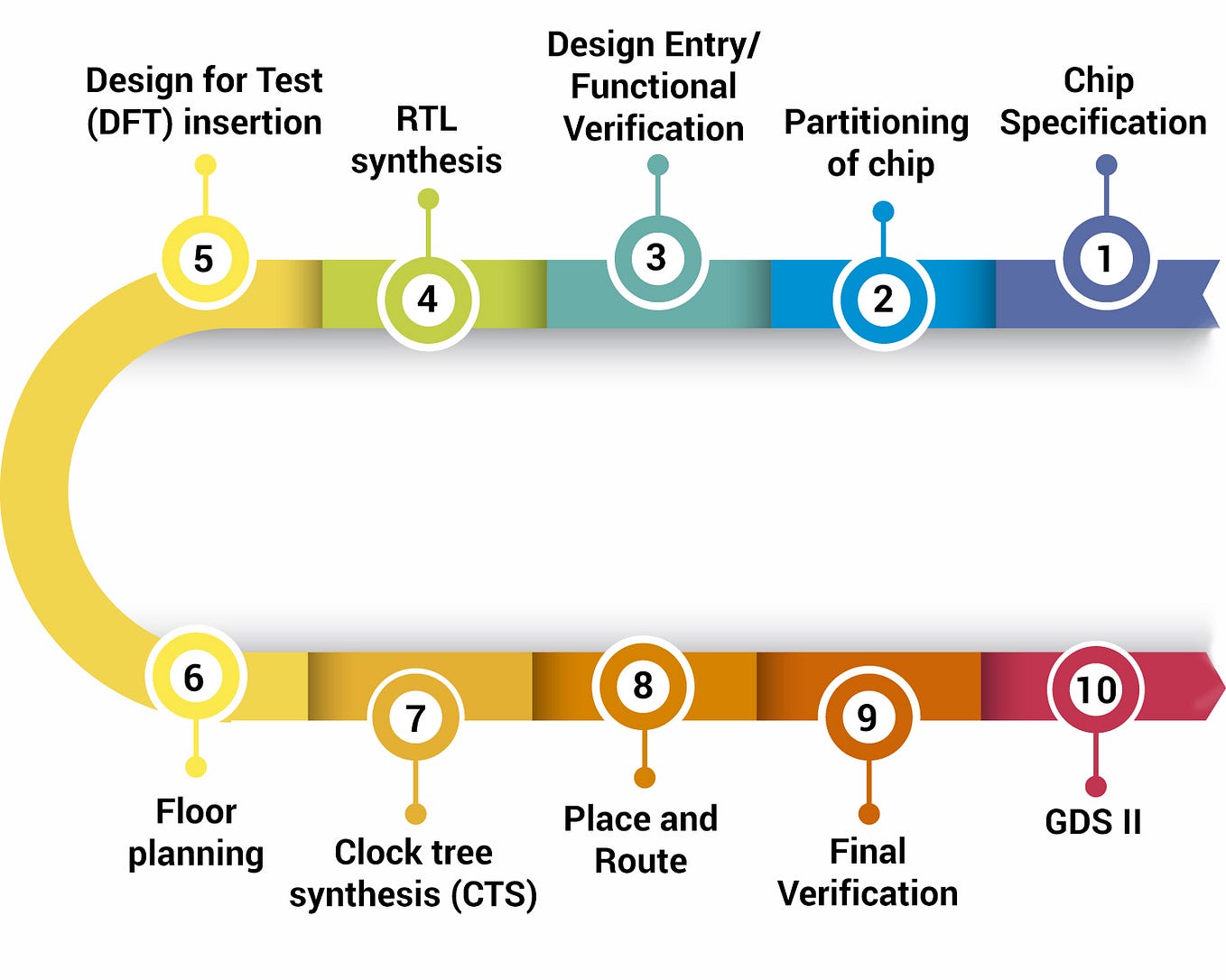

Introduction To System Verilog Assertions And Functional Coverage The verification plan includes a test plan (list of test cases that target design features), functional coverage planning, module block assignments to the verification engineers, checker, and assertion planning. Initially, at the level b, bugs can be caught using the directed testcase. however, once the bug count starts dropping, it’s time to introduce corner cases, functional coverage, and assertions. Plans: what is a verification requirement? the serial receive block has four buffers. the block checks for the parity and validity of the data frame on the rxd input and then writes correct data into its buffers. check that rxd data is being properly written into buffers taking into consideration the parity and validity of the data. Learn assertion based verification in vlsi with real systemverilog examples. understand abv concepts, benefits, and best practices for verification engineers. A typical asic design flow follows a structured methodology broken down into multiple stages. some phases happen in parallel (e.g., design and verification), while others are sequential (e.g., synthesis must follow rtl design). We propose an automatic assertion generation framework using retrieval augmented generation (rag) and llms. it generates assertions from designer tailored specifications, ensuring conformance with high level specifications and reducing hallucinations.

System Verilog Assertions Simplified By Einfochips An Arrow Company Plans: what is a verification requirement? the serial receive block has four buffers. the block checks for the parity and validity of the data frame on the rxd input and then writes correct data into its buffers. check that rxd data is being properly written into buffers taking into consideration the parity and validity of the data. Learn assertion based verification in vlsi with real systemverilog examples. understand abv concepts, benefits, and best practices for verification engineers. A typical asic design flow follows a structured methodology broken down into multiple stages. some phases happen in parallel (e.g., design and verification), while others are sequential (e.g., synthesis must follow rtl design). We propose an automatic assertion generation framework using retrieval augmented generation (rag) and llms. it generates assertions from designer tailored specifications, ensuring conformance with high level specifications and reducing hallucinations.

Comments are closed.