Area Delay Efficient Binary Adders In Qca Pdf

Design Of The Best Area Delay Adders With Qca Majority Logic Gates By In this brief, an innovative technique is presented to implement high speed low area adders into qca.theoretical formulations established for cla and parallel prefix adders are here exploited for the realization of a novel2 bit addition slice. In this brief, an innovative technique is presented to implement high speed low area adders into qca. theoretical formulations established for cla and parallel prefix adders are here exploited for the realization of a novel 2 bit addition slice.

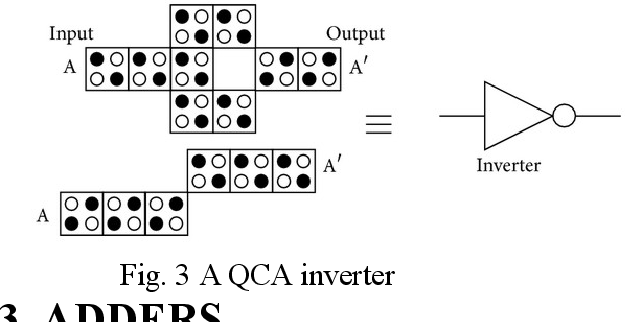

Figure 3 From Area Delay Dynamic Binary Adders In Qca Semantic Scholar In this brief, an innovative technique is presented to implement high speed low area adders into qca. theoretical formulations established for cla and parallel prefix adders are here exploited for the realize of a novel 2 bit addition slice. In this article, we expand this research to understand radical right parties' environmental issue emphasis and what explains this increasing emphasis. we argue that radical right parties engage in a two pronged strategy of responsiveness and differentiation on the environment. The qca architecture is therefore, low area, low delay, simple and efficient for vlsi hardware implementation. it would be interesting to test the design of the modified 128 bit novel adders. In this brief, we propose a new adder that outperforms all state of the art competitors and achieves the best area delay tradeoff. the above advantages are obtained by using an overall area similar to the cheaper designs known in literature.

Comparison Of Different Qca Full Adders Download Scientific Diagram The qca architecture is therefore, low area, low delay, simple and efficient for vlsi hardware implementation. it would be interesting to test the design of the modified 128 bit novel adders. In this brief, we propose a new adder that outperforms all state of the art competitors and achieves the best area delay tradeoff. the above advantages are obtained by using an overall area similar to the cheaper designs known in literature. In this brief, we propose a new adder that achieve the better area delay trade off compared to the design known in literature. the simulations in the present work have been carried out using qcadesigner tool. In this brief, we propose a new adder that outperforms all state of theart competitors and achieves the best area delay tradeoff. the above advantages are obtained by using an overall area similar to the cheaper designs known in literature. An innovative technique is presented to implement high speed low area adders in qca. theoretical formulations demonstrated for cla adders are here exploited for the realization of a novel 2 bit addition slice. A 64 bit binary adder designed as described in this brief exhibited a delay and occupied an active area. it achieved speed performances higher than all the existing qca adders, with an area requirement comparable.

Comments are closed.