Adder Design Using Qca Technique With Area Delay Efficient Open

Efficient Designs Of Qca Full Adder And 4 Bit Qca Pdf Logic Gate A novel quantum dot cellular automata (qca) adder design is presented that reduces the number of qca cells compared to previously reported designs. the proposed one bit qca adder structure is based on a new algorithm that requires only three majority gates and two inverters for the qca addition. This paper presents a novel low delay 4 bit parallel prefix adder (ppa) implemented as a multilayer circuit using quantum dot cellular automata (qca) technology.

Pdf Novel Efficient Scalable Qca Xor And Full Adder Designs In this chapter, we discuss two different designs of qca ripple carry adders by customizing the fundamental block, i.e., the full adder circuit. we start the discussion with designing rca using 5 input majority gate based full adder. In this brief, we propose a new adder that outperforms all state of the art competitors and achieves the best area delay tradeoff. the above advantages are obtained by using an overall area similar to the cheaper designs known in literature. This paper proposes novel energy and ultra area efficient qca technology based full adder designs, as well as a review of the various adder circuit layout designs. in terms of cell count, area, and power dissipation, the proposed design is more sophisticated than traditional designs. For this reason the designing of logic circuits in qca draws much attention nowadays. the fundamental arithmetic operation is addition and sev omata, which is an array of coupled quantum dots to implement boolean logic functions. of course, the architectures commonly employed in tr.

Design And Development Of 4 Bit Adder Programmable Qca Design Using Alu This paper proposes novel energy and ultra area efficient qca technology based full adder designs, as well as a review of the various adder circuit layout designs. in terms of cell count, area, and power dissipation, the proposed design is more sophisticated than traditional designs. For this reason the designing of logic circuits in qca draws much attention nowadays. the fundamental arithmetic operation is addition and sev omata, which is an array of coupled quantum dots to implement boolean logic functions. of course, the architectures commonly employed in tr. In this paper, an optimal adder circuit is proposed using qca technology which consist only 14 cells. the proposed adder circuit is further utilised for designing of 4 bit adder design efficiently. Leveraging the unique features of qca, such as the absence of current flow and the potential for highly compact layouts, we present a detailed design methodology for the bcd adder circuit, including the implementation of basic qca gates and construction of the bcd addition logic. In this section, these previously designed qca full adder circuits will be investigated based on their complexity, wire crossing type, area requirement, delay, and quantum cost. Design of the best area delay adders with qca majority logic gates by using vhdl free download as pdf file (.pdf), text file (.txt) or read online for free.

Proposed Half Adder Cell Design In Qca Download Scientific Diagram In this paper, an optimal adder circuit is proposed using qca technology which consist only 14 cells. the proposed adder circuit is further utilised for designing of 4 bit adder design efficiently. Leveraging the unique features of qca, such as the absence of current flow and the potential for highly compact layouts, we present a detailed design methodology for the bcd adder circuit, including the implementation of basic qca gates and construction of the bcd addition logic. In this section, these previously designed qca full adder circuits will be investigated based on their complexity, wire crossing type, area requirement, delay, and quantum cost. Design of the best area delay adders with qca majority logic gates by using vhdl free download as pdf file (.pdf), text file (.txt) or read online for free.

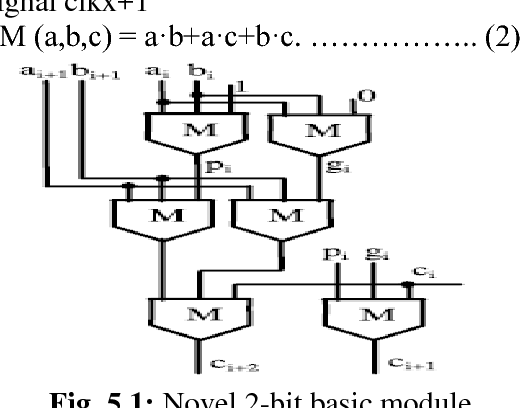

Figure 5 1 From Design Of The Best Area Delay Adders With Qca Majority In this section, these previously designed qca full adder circuits will be investigated based on their complexity, wire crossing type, area requirement, delay, and quantum cost. Design of the best area delay adders with qca majority logic gates by using vhdl free download as pdf file (.pdf), text file (.txt) or read online for free.

Design Of The Best Area Delay Adders With Qca Majority Logic Gates By

Comments are closed.