A Mapping Design Tips Pdf Cache Computing Cpu Cache

Cache Mapping Pdf Cpu Cache Random Access Memory A mapping design tips free download as word doc (.doc), pdf file (.pdf), text file (.txt) or read online for free. this document provides tips for optimizing powercenter mappings and using mapplets. Answer: a n way set associative cache is like having n direct mapped caches in parallel.

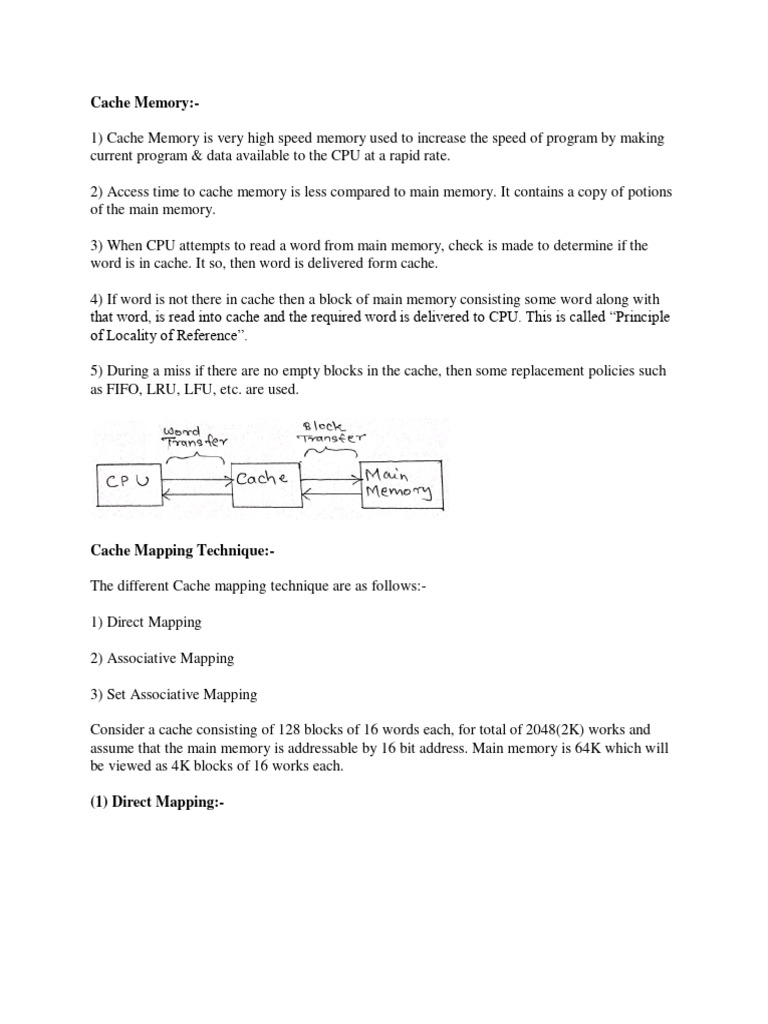

03 Chap4 Cache Memory Mapping Pdf Cpu Cache Computer Data Storage Two questions to answer (in hardware) q1 how do we know if a data item is in the cache? q2 if it is, how do we find it?. How can we exploit locality to bridge the cpu memory gap? use it to determine which data to put in a cache! spatial locality when level k needs a byte from level k 1, don’t just bring one byte bring neighboring bytes as well! good chances we’ll need them too in the near future. Why do we cache? use caches to mask performance bottlenecks by replicating data closer. The simplest technique, known as direct mapping, maps each block of main memory into only one possible cache line. figure 5.6a shows the mapping for the first m blocks of main memory.

Cache Memory Pdf Cpu Cache Information Technology Why do we cache? use caches to mask performance bottlenecks by replicating data closer. The simplest technique, known as direct mapping, maps each block of main memory into only one possible cache line. figure 5.6a shows the mapping for the first m blocks of main memory. What to do then? any ideas? typically, a computer has a hierarchy of memory subsystems:. How should space be allocated to threads in a shared cache? should we store data in compressed format in some caches? how do we do better reuse prediction & management in caches?. The most important element in the on chip memory system is the notion of a cache that stores a subset of the memory space, and the hierarchy of caches. in this section, we assume that the reader is well aware of the basics of caches, and is also aware of the notion of virtual memory. Designing for high performance requires considering the restrictions of the memory hierarchy, i.e. the size and capabilities of each component. the memory hierarchy separates computer storage.

Elements Of Cache Design Pentium Iv Cache Organization Pdf Cpu What to do then? any ideas? typically, a computer has a hierarchy of memory subsystems:. How should space be allocated to threads in a shared cache? should we store data in compressed format in some caches? how do we do better reuse prediction & management in caches?. The most important element in the on chip memory system is the notion of a cache that stores a subset of the memory space, and the hierarchy of caches. in this section, we assume that the reader is well aware of the basics of caches, and is also aware of the notion of virtual memory. Designing for high performance requires considering the restrictions of the memory hierarchy, i.e. the size and capabilities of each component. the memory hierarchy separates computer storage.

Cache Mapping Easyexamnotes The most important element in the on chip memory system is the notion of a cache that stores a subset of the memory space, and the hierarchy of caches. in this section, we assume that the reader is well aware of the basics of caches, and is also aware of the notion of virtual memory. Designing for high performance requires considering the restrictions of the memory hierarchy, i.e. the size and capabilities of each component. the memory hierarchy separates computer storage.

Comments are closed.