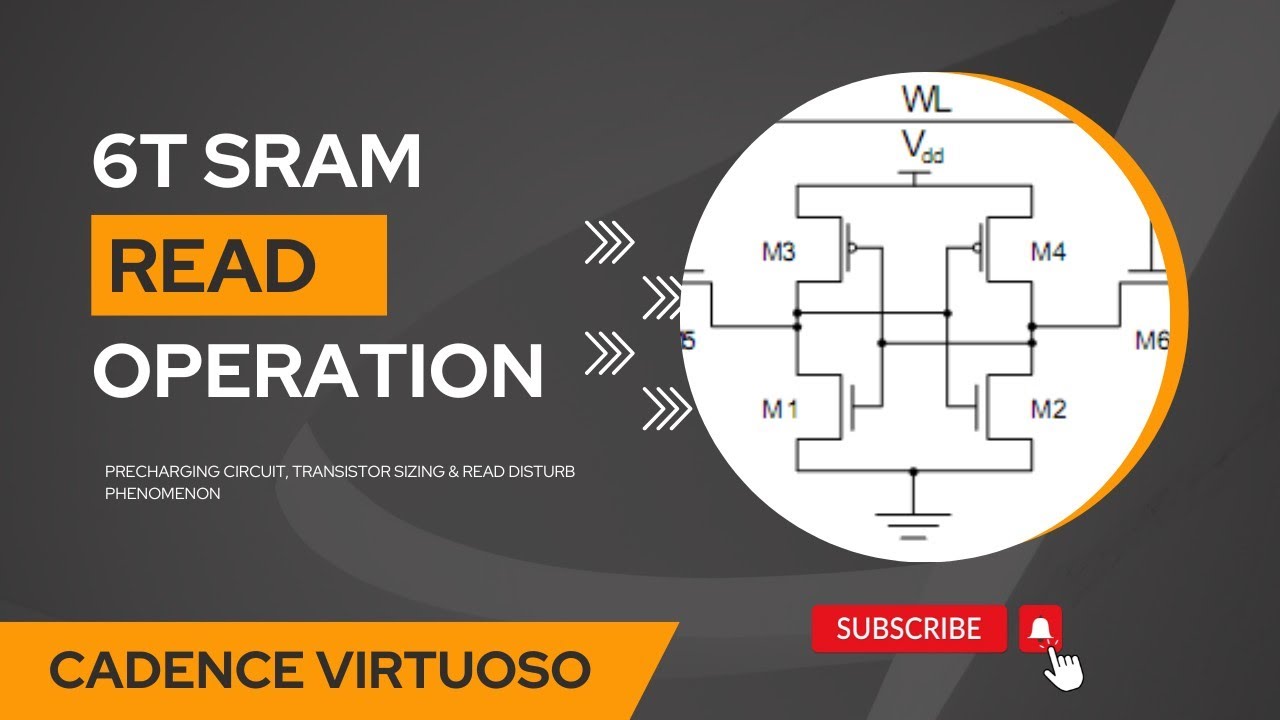

6t Sram Read Operation Explained 90nm Technology Cadence Virtuoso Simulation Tutorial

Detailed 6t Sram Read Simulation In Cadence Virtuoso Transistor Sizing Learn the read operation of a 6t sram cell in 90nm cmos technology using cadence virtuoso. Designing a 6t sram cell in cadence virtuoso offers hands on experience in memory circuit design and simulation. by following these steps and analyzing the butterfly curve, you’ll gain a deep understanding of sram stability and performance.

Design Of Sram 6t Cell Using Stacking Effect In Cadence Virtuoso Youtube Master the schematic design and simulation of a 6t sram cell using the older cadence virtuoso environment with 90nm gpdk technology. this 6 part series walks you through every step —. In this video, i demonstrate the complete schematic design and simulation of a 6t sram (static random access memory) cell using [tool name – e.g., cadence virtuoso tanner eda]. more. Discover the complete process of simulating a 6t sram read operation using cadence virtuoso in this in depth tutorial. This project focuses on the transistor level design and simulation of a 6 transistor (6t) static random access memory (sram) cell using cadence virtuoso. the 6t sram is a widely used memory element in digital systems due to its speed, low power consumption, and stability.

Sram 6t Read 0 And Read 1 Operation In Cadence Virtuoso Youtube Discover the complete process of simulating a 6t sram read operation using cadence virtuoso in this in depth tutorial. This project focuses on the transistor level design and simulation of a 6 transistor (6t) static random access memory (sram) cell using cadence virtuoso. the 6t sram is a widely used memory element in digital systems due to its speed, low power consumption, and stability. In this paper performance evaluation of 6t sram cell topology has been carried out using cadence virtuoso tools in a 90 nm technology node. it is performed in terms of the read and write operations, power, noise, temperature, and also the hold operations have been analyzed. This project presents the design and functional validation of a 6 transistor (6t) sram cell at the transistor level using cadence virtuoso. the objective was to understand sram cell operation, read write behavior, and stability using an industry standard vlsi design environment. 6t cell consists of two back to back connected inverters and two access transistors. for the design of 6t cell first we need to understand the operation and behaviour of the 6 transistors involved in the design. Abstract—this project presents the design and implementation of a static random access memory (sram) system using the cadence virtuoso. sram is a key component in modern digital systems, particularly in cache memory, due to its high speed, low latency, and low static power consumption.

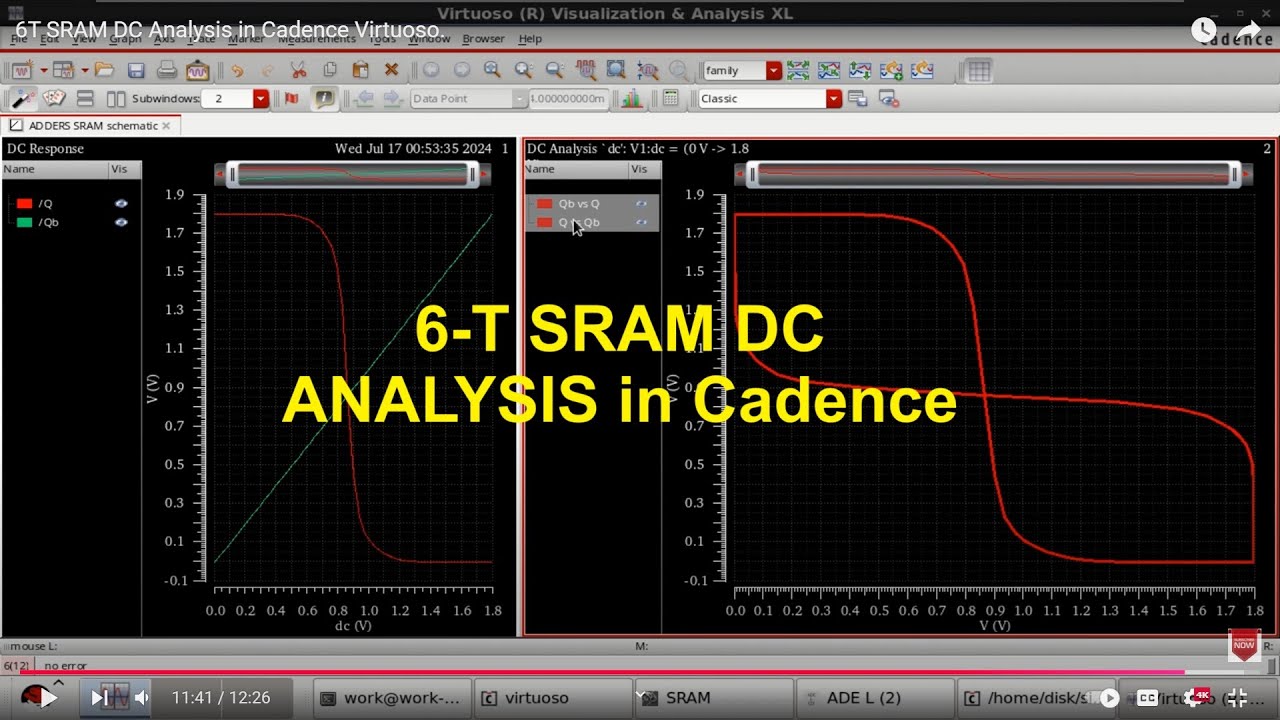

6t Sram Dc Analysis In Cadence Virtuoso Youtube In this paper performance evaluation of 6t sram cell topology has been carried out using cadence virtuoso tools in a 90 nm technology node. it is performed in terms of the read and write operations, power, noise, temperature, and also the hold operations have been analyzed. This project presents the design and functional validation of a 6 transistor (6t) sram cell at the transistor level using cadence virtuoso. the objective was to understand sram cell operation, read write behavior, and stability using an industry standard vlsi design environment. 6t cell consists of two back to back connected inverters and two access transistors. for the design of 6t cell first we need to understand the operation and behaviour of the 6 transistors involved in the design. Abstract—this project presents the design and implementation of a static random access memory (sram) system using the cadence virtuoso. sram is a key component in modern digital systems, particularly in cache memory, due to its high speed, low latency, and low static power consumption.

6t Sram Read Operation Explained 90nm Technology Cadence Virtuoso 6t cell consists of two back to back connected inverters and two access transistors. for the design of 6t cell first we need to understand the operation and behaviour of the 6 transistors involved in the design. Abstract—this project presents the design and implementation of a static random access memory (sram) system using the cadence virtuoso. sram is a key component in modern digital systems, particularly in cache memory, due to its high speed, low latency, and low static power consumption.

Comments are closed.