6t Sram Dc Analysis In Cadence Virtuoso

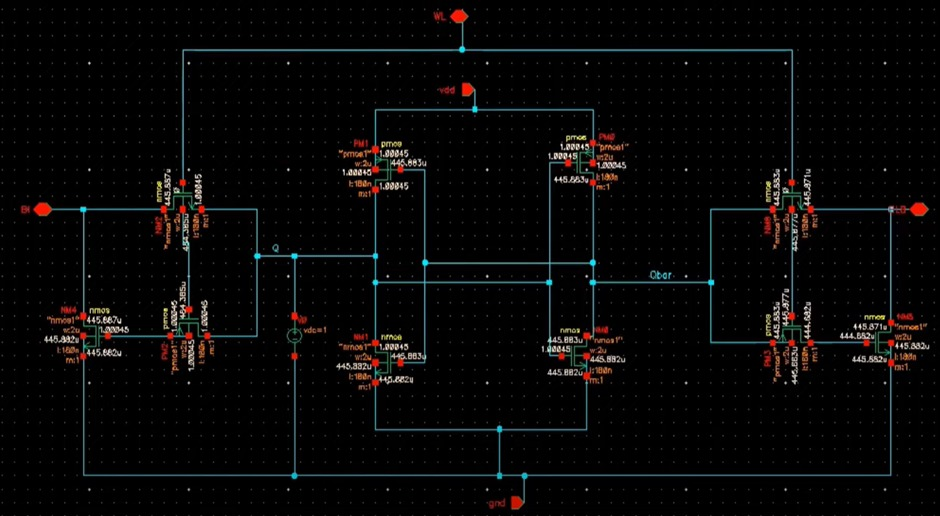

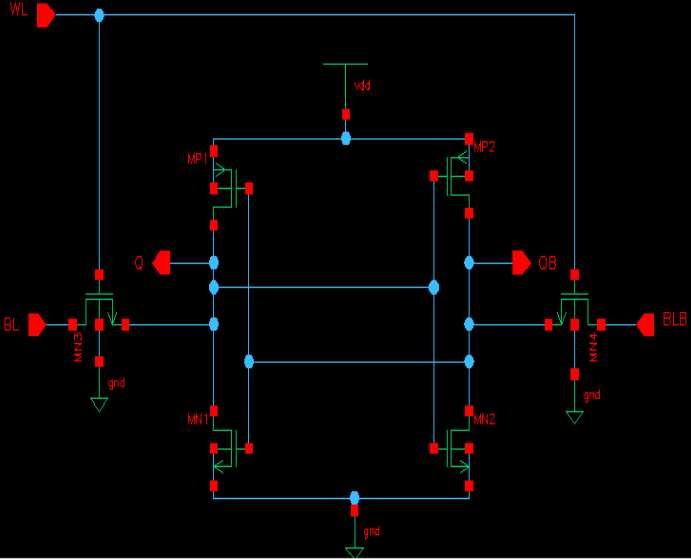

Github Jayaram998 Designing And Simulating A 6t Sram Cell In Cadence This paper presents the design and analysis of a low power 6 transistor (6t) static random access memory (sram) cell using 180nm cmos technology in the cadence virtuoso environment. This project presents the design, layout, and comparative analysis of 6t, 7t, and 8t static random access memory (sram) cells. the cells were designed in cadence virtuoso using a 180nm cmos technology.

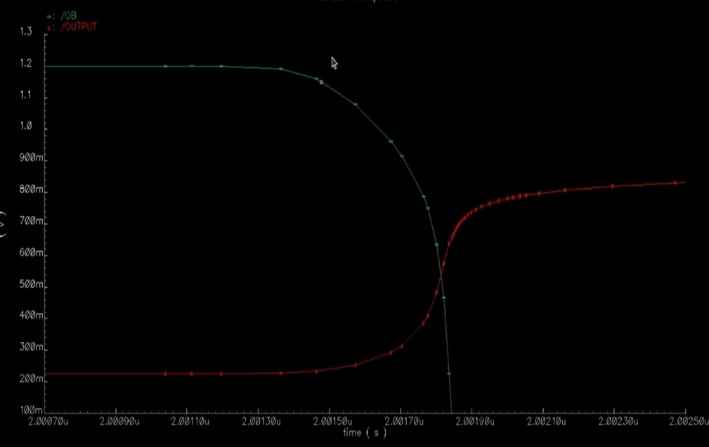

Improving The Sram Layout Design Using Cadence Virtuoso Abstract—this project presents the design and implementation of a static random access memory (sram) system using the cadence virtuoso. sram is a key component in modern digital systems, particularly in cache memory, due to its high speed, low latency, and low static power consumption. In this paper, the design and analysis of cmos based 6t sram cell at different technology nodes is demonstrated. This research investigates the performance optimization of a 6t sram cell design in 90nm and 45nm technologies. focused on reducing both power consumption, acce. This video shows the design and dc analysis of a 6t sram cell in cadence virtuoso.

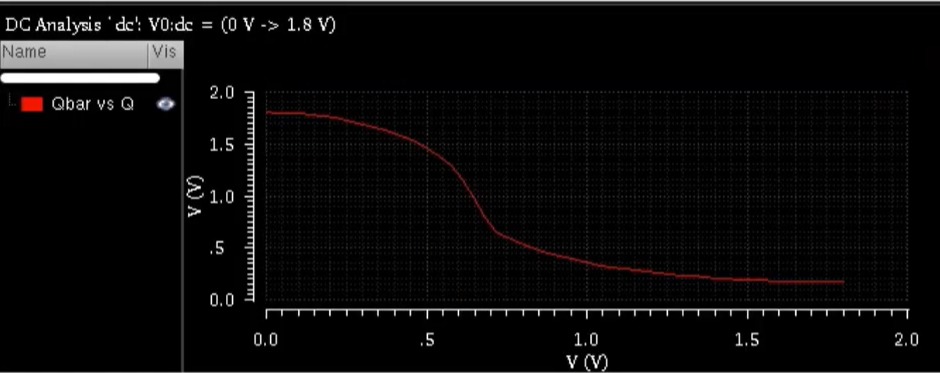

Improving The Sram Layout Design Using Cadence Virtuoso This research investigates the performance optimization of a 6t sram cell design in 90nm and 45nm technologies. focused on reducing both power consumption, acce. This video shows the design and dc analysis of a 6t sram cell in cadence virtuoso. In this paper, design and performance analysis of a 6t sram cell is discussed. performance analysis is carried out by using cadence virtuoso in 180nm cmos technology. This paper presents design and implementation of 16bit 6t sram using different cmos technologies using cadence virtuoso tool. due to the requirement of more storage, usage of 16 bit sram is convenient. To design a 6 bit sram cell using cadence virtuoso at 180nm technology, perform dc analysis, and plot the butterfly curve to evaluate the static noise margin (snm). This paper introduces an optimized method for sram layout design with cadence virtuoso for 6t, 7t, 8t, and 10t sram cells to improve their performance in power constrained and high speed applications.

Improving The Sram Layout Design Using Cadence Virtuoso In this paper, design and performance analysis of a 6t sram cell is discussed. performance analysis is carried out by using cadence virtuoso in 180nm cmos technology. This paper presents design and implementation of 16bit 6t sram using different cmos technologies using cadence virtuoso tool. due to the requirement of more storage, usage of 16 bit sram is convenient. To design a 6 bit sram cell using cadence virtuoso at 180nm technology, perform dc analysis, and plot the butterfly curve to evaluate the static noise margin (snm). This paper introduces an optimized method for sram layout design with cadence virtuoso for 6t, 7t, 8t, and 10t sram cells to improve their performance in power constrained and high speed applications.

Cadence Virtuoso Ultimate Guide To design a 6 bit sram cell using cadence virtuoso at 180nm technology, perform dc analysis, and plot the butterfly curve to evaluate the static noise margin (snm). This paper introduces an optimized method for sram layout design with cadence virtuoso for 6t, 7t, 8t, and 10t sram cells to improve their performance in power constrained and high speed applications.

Solved There Is A 6t Sram Static Random Access Memory Chegg

Comments are closed.