6t Sram Cell Schematic Design Simulation In Cadence Virtuoso Vlsi Project Tutorial

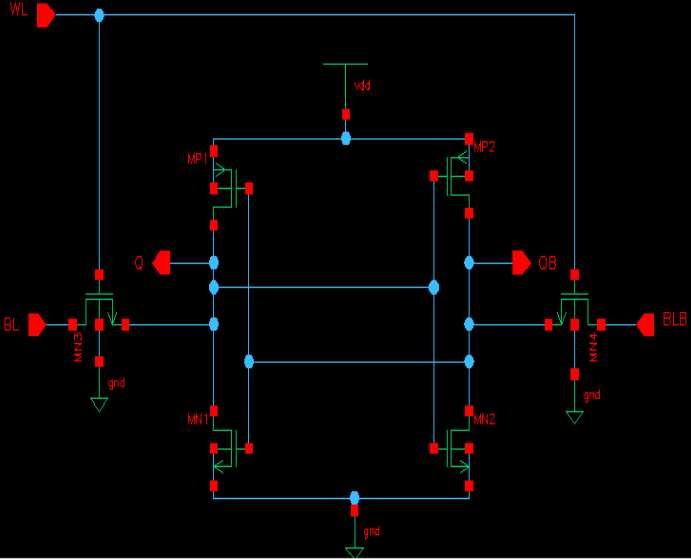

Design And Simulation Of 6t Sram Cell Architectures In 32nm Technology In this video, i demonstrate the complete schematic design and simulation of a 6t sram (static random access memory) cell using [tool name – e.g., cadence virtuoso tanner eda] . Designing a 6t sram cell in cadence virtuoso offers hands on experience in memory circuit design and simulation. by following these steps and analyzing the butterfly curve, you’ll gain a deep understanding of sram stability and performance.

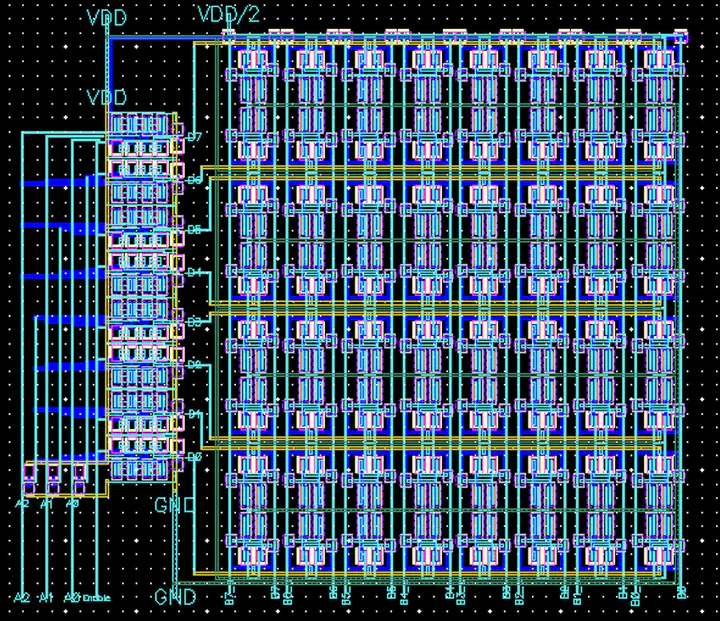

Github Jayaram998 Designing And Simulating A 6t Sram Cell In Cadence This work presents the complete design, simulation, and layout verification of a low power 6t sram cell using 180nm cmos technology in the cadence virtuoso environment. The project successfully demonstrates the key aspects of sram design at the schematic level, highlighting the role of supporting circuits in enhancing memory reliability and operations. As part of my digital vlsi design course, i developed a 1 kilobyte (32×32) 6t sram array from schematic to layout using cadence virtuoso. this included designing and verifying memory cells, integrating a 5 to 32 decoder for wordline selection, and optimizing the layout for performance and area. Explore the design and analysis of a 6t sram cell using 180nm cmos technology, emphasizing stability and power efficiency in cadence virtuoso.

6t Sram Memory Cell Design And Layout Dias Azhigulov As part of my digital vlsi design course, i developed a 1 kilobyte (32×32) 6t sram array from schematic to layout using cadence virtuoso. this included designing and verifying memory cells, integrating a 5 to 32 decoder for wordline selection, and optimizing the layout for performance and area. Explore the design and analysis of a 6t sram cell using 180nm cmos technology, emphasizing stability and power efficiency in cadence virtuoso. We’ll explore how the verified 6t cell is expanded into a complete sram array, focusing on cell organization, peripheral circuitry, and array level performance optimization. Master the schematic design and simulation of a 6t sram cell using the older cadence virtuoso environment with 90nm gpdk technology. this 6 part series walks you through every step. 🎓 welcome to this complete tutorial on 6t sram cell design using cadence virtuoso with gpdk 45nm technology. in this video, you’ll learn how to design, simulate, and analyze a 6t. This project presents the design, layout, and comparative analysis of 6t, 7t, and 8t static random access memory (sram) cells. the cells were designed in cadence virtuoso using a 180nm cmos technology.

Solved There Is A 6t Sram Static Random Access Memory Chegg We’ll explore how the verified 6t cell is expanded into a complete sram array, focusing on cell organization, peripheral circuitry, and array level performance optimization. Master the schematic design and simulation of a 6t sram cell using the older cadence virtuoso environment with 90nm gpdk technology. this 6 part series walks you through every step. 🎓 welcome to this complete tutorial on 6t sram cell design using cadence virtuoso with gpdk 45nm technology. in this video, you’ll learn how to design, simulate, and analyze a 6t. This project presents the design, layout, and comparative analysis of 6t, 7t, and 8t static random access memory (sram) cells. the cells were designed in cadence virtuoso using a 180nm cmos technology.

Comments are closed.