5 Uart Parity Bit And Error Detection

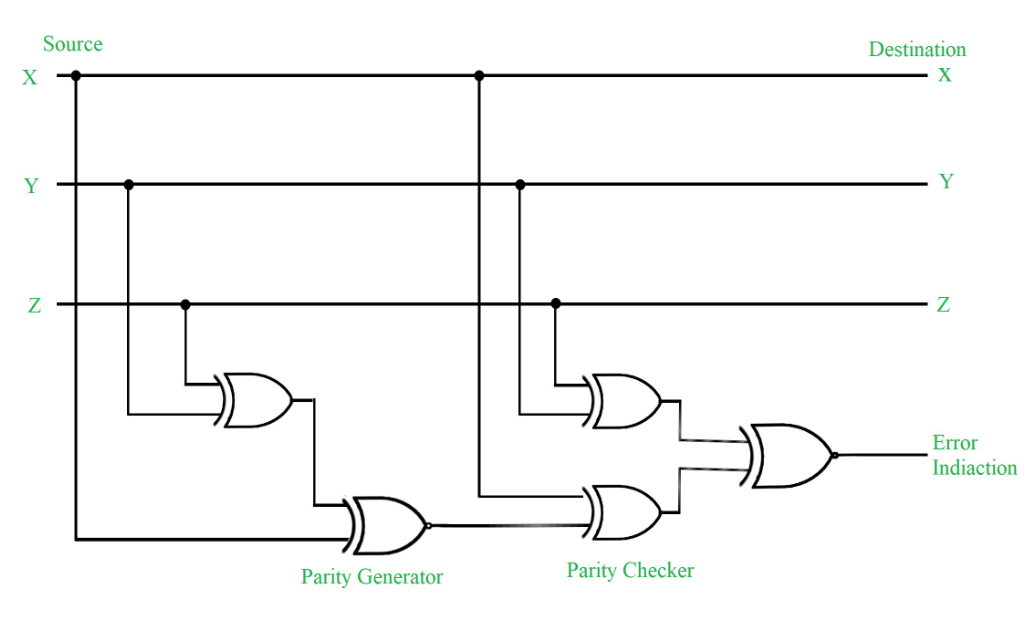

Error Detection Codes Parity Bit Geeksforgeeks Implementing a parity bit check in uart communication enhances the reliability of data transfer by detecting potential errors. while it is not foolproof and cannot correct errors, it provides a cost effective and straightforward method for error detection. Data word bits, along with parity bits, are called a codeword. the parity bit is added to the message bits on the sender side to help in error detection at the receiver side.

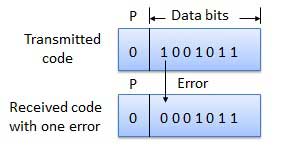

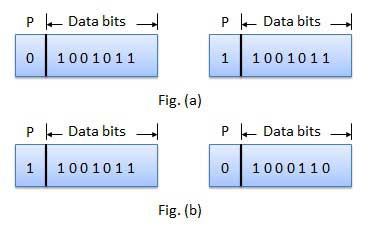

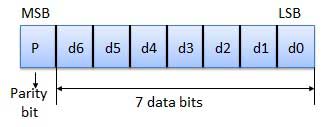

Error Detection Codes Parity Bit Geeksforgeeks While the parity bit is useful, it only detects single bit errors. it can't catch more complex errors, such as when multiple bits are flipped. Uart (universal asynchronous receiver transmitter) sends data in a structured frame that includes the following components: start bit: always 0; indicates the beginning of the frame. data bits: the actual payload, typically 5 to 8 bits. parity bit(optional): used for simple error detection. It ensures that the total number of 1 bits in the data (including the parity bit itself) is either even (even parity) or odd (odd parity). this method is widely used in computer memory (ram ecc basics), serial communication protocols (uart, rs 232), and legacy data transmission systems to detect single bit errors caused by electrical noise. Uart parity example parity provides single bit error detection (optional) parity options are even, odd, none.

Read About Parity Bit Error Detection In Detail Techyv It ensures that the total number of 1 bits in the data (including the parity bit itself) is either even (even parity) or odd (odd parity). this method is widely used in computer memory (ram ecc basics), serial communication protocols (uart, rs 232), and legacy data transmission systems to detect single bit errors caused by electrical noise. Uart parity example parity provides single bit error detection (optional) parity options are even, odd, none. The uart transmitter and receiver also includes parity checking for both even and odd, so users can use the maximum number of combination (256 unique combinations) of the 8 bit data that gets sent, while providing error checking. When the parity bit matches the data, the uart knows that the transmission was free of errors. but if the parity bit is a 0, and the total is odd, or the parity bit is a 1, and the total is even, the uart knows that bits in the data frame have changed. In multiprocessor configurations it is often desirable that only the intended message recipient should actively receive the full message contents, thus reducing redundant usart service overhead for all non addressed receivers. 𝑭𝒓𝒂𝒎𝒆 𝑭𝒐𝒓𝒎𝒂𝒕: uart transmits data in frames, consisting of a start bit (1), data bits (ranging from 5 to 9), an optional parity bit for error detection, and a stop bit (1 or.

Read About Parity Bit Error Detection In Detail Techyv The uart transmitter and receiver also includes parity checking for both even and odd, so users can use the maximum number of combination (256 unique combinations) of the 8 bit data that gets sent, while providing error checking. When the parity bit matches the data, the uart knows that the transmission was free of errors. but if the parity bit is a 0, and the total is odd, or the parity bit is a 1, and the total is even, the uart knows that bits in the data frame have changed. In multiprocessor configurations it is often desirable that only the intended message recipient should actively receive the full message contents, thus reducing redundant usart service overhead for all non addressed receivers. 𝑭𝒓𝒂𝒎𝒆 𝑭𝒐𝒓𝒎𝒂𝒕: uart transmits data in frames, consisting of a start bit (1), data bits (ranging from 5 to 9), an optional parity bit for error detection, and a stop bit (1 or.

Read About Parity Bit Error Detection In Detail Techyv In multiprocessor configurations it is often desirable that only the intended message recipient should actively receive the full message contents, thus reducing redundant usart service overhead for all non addressed receivers. 𝑭𝒓𝒂𝒎𝒆 𝑭𝒐𝒓𝒎𝒂𝒕: uart transmits data in frames, consisting of a start bit (1), data bits (ranging from 5 to 9), an optional parity bit for error detection, and a stop bit (1 or.

Comments are closed.