4 1 1 5 Core Feature Vectored Interrupt Nuclei Board Labs 0 1 0

What Is An Vectored Interrupt Computer Science 2 Pdf Explanation: if the interrupt is set to vectored processing mode, once it’s taken, the processor core will jump to the target address saved in the vector table entry directly, which is the corresponding interrupt service routine of the interrupt. The hierarchy of nuclei board labs are shown in the block diagram below. the labs are developed based on the nuclei software development kit (nuclei sdk) which is an open software platform to facilitate the software development of systems based on nuclei processor cores.

Question Answers Vectored Interrupt Vs Non Vectored Interrupt Core feature: nesting of interrupts. 4.1.1.5. core feature: vectored interrupt. 4.1.2. advanced labs. 4.1.2.1. nuclei sdk demos. Core feature: nesting of interrupts. 4.1.1.5. core feature: vectored interrupt. Core feature: interrupt. 4.1.1.4. core feature: nesting of interrupts. 4.1.1.5. core feature: vectored interrupt. 4.1.2. advanced labs. 5. changelog. 6. appendix. 7. glossary. 4. hands on labs » 4.1. rv star development board » 4.1.1. basic labs. 4.1.1. basic labs ¶. The hierarchy of nuclei board labs are shown in the block diagram below. the labs are developed based on the nuclei software development kit (nuclei sdk) which is an open software platform to facilitate the software development of systems based on nuclei processor cores.

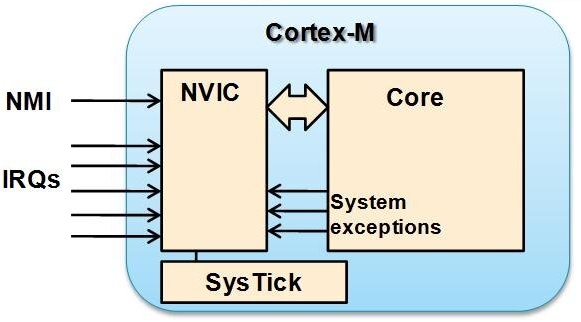

Question Answers Vectored Interrupt Vs Non Vectored Interrupt Core feature: interrupt. 4.1.1.4. core feature: nesting of interrupts. 4.1.1.5. core feature: vectored interrupt. 4.1.2. advanced labs. 5. changelog. 6. appendix. 7. glossary. 4. hands on labs » 4.1. rv star development board » 4.1.1. basic labs. 4.1.1. basic labs ¶. The hierarchy of nuclei board labs are shown in the block diagram below. the labs are developed based on the nuclei software development kit (nuclei sdk) which is an open software platform to facilitate the software development of systems based on nuclei processor cores. It details the types of interrupts, the role of the nested vectored interrupt controller (nvic), and how to program interrupts using registers. additionally, it includes exercises for practical application using the nucleo f401re board. A nested vectored interrupt controller is used to manage the interrupts from multiple interrupt sources. nvic is closely integrated with the processor core to achieve low latency interrupt processing and efficient processing of late arriving interrupts. This article focuses on building a small example in c to implement vectored interrupt handling for any risc v core. i’ve used this technique for deeply embedded firmware on minimal risc v cores. It explains the advantages of vectored interrupts over non vectored interrupts. it shows how to configure the vector interrupt controllers (vics) for vectored interrupts and demonstrates vectored interrupts processing by example programs.

In A Vectored Interrupt Ashrafedu It details the types of interrupts, the role of the nested vectored interrupt controller (nvic), and how to program interrupts using registers. additionally, it includes exercises for practical application using the nucleo f401re board. A nested vectored interrupt controller is used to manage the interrupts from multiple interrupt sources. nvic is closely integrated with the processor core to achieve low latency interrupt processing and efficient processing of late arriving interrupts. This article focuses on building a small example in c to implement vectored interrupt handling for any risc v core. i’ve used this technique for deeply embedded firmware on minimal risc v cores. It explains the advantages of vectored interrupts over non vectored interrupts. it shows how to configure the vector interrupt controllers (vics) for vectored interrupts and demonstrates vectored interrupts processing by example programs.

Nuclei Pdf This article focuses on building a small example in c to implement vectored interrupt handling for any risc v core. i’ve used this technique for deeply embedded firmware on minimal risc v cores. It explains the advantages of vectored interrupts over non vectored interrupts. it shows how to configure the vector interrupt controllers (vics) for vectored interrupts and demonstrates vectored interrupts processing by example programs.

Vectored Interrupt Controller Vic And Nvic

Comments are closed.