4 1 1 4 Core Feature Nesting Of Interrupts Nuclei Board Labs 0 1 0

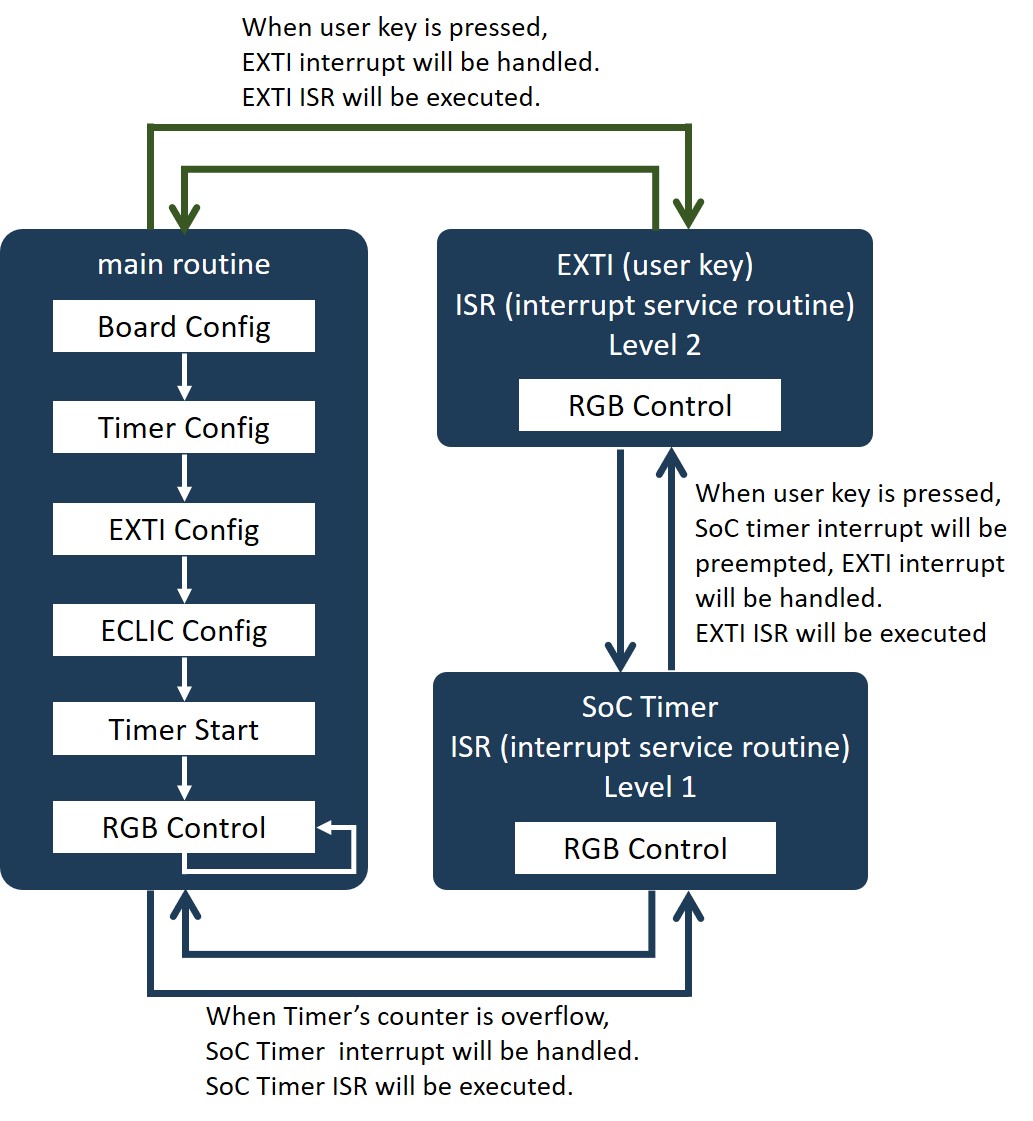

Nuclei Pdf In this lab, we just show how to implement nesting of non vectored interrupt. about how to implement nesting of vectored interrupt, please refer to core feature: vectored interrupt. Core feature: nesting of interrupts. 4.1.1.5. core feature: vectored interrupt. 4.1.2. advanced labs. 4.1.2.1. nuclei sdk demos.

4 1 1 4 Core Feature Nesting Of Interrupts Nuclei Board Labs 0 1 0 How to use nuclei board. 4.1.1.2. soc peripheral: timer. 4.1.1.3. core feature: interrupt. 4.1.1.4. core feature: nesting of interrupts. 4.1.1.5. core feature: vectored interrupt. 4.1.2. advanced labs. 5. changelog. 6. appendix. 7. glossary. 4. hands on labs » 4.1. rv star development board » 4.1.1. basic labs. 4.1.1. basic labs ¶. The hierarchy of nuclei board labs are shown in the block diagram below. the labs are developed based on the nuclei software development kit (nuclei sdk) which is an open software platform to facilitate the software development of systems based on nuclei processor cores. The hierarchy of nuclei board labs are shown in the block diagram below. the labs are developed based on the nuclei software development kit (nuclei sdk) which is an open software platform to facilitate the software development of systems based on nuclei processor cores. Core feature: interrupt; 4.then the main stack must have space for 3 exception frames plus however many levels of nested interrupts (i usual only use 1, so no interrupt nesting) plus the stack usage by the handlers (which the compiler will estimate).

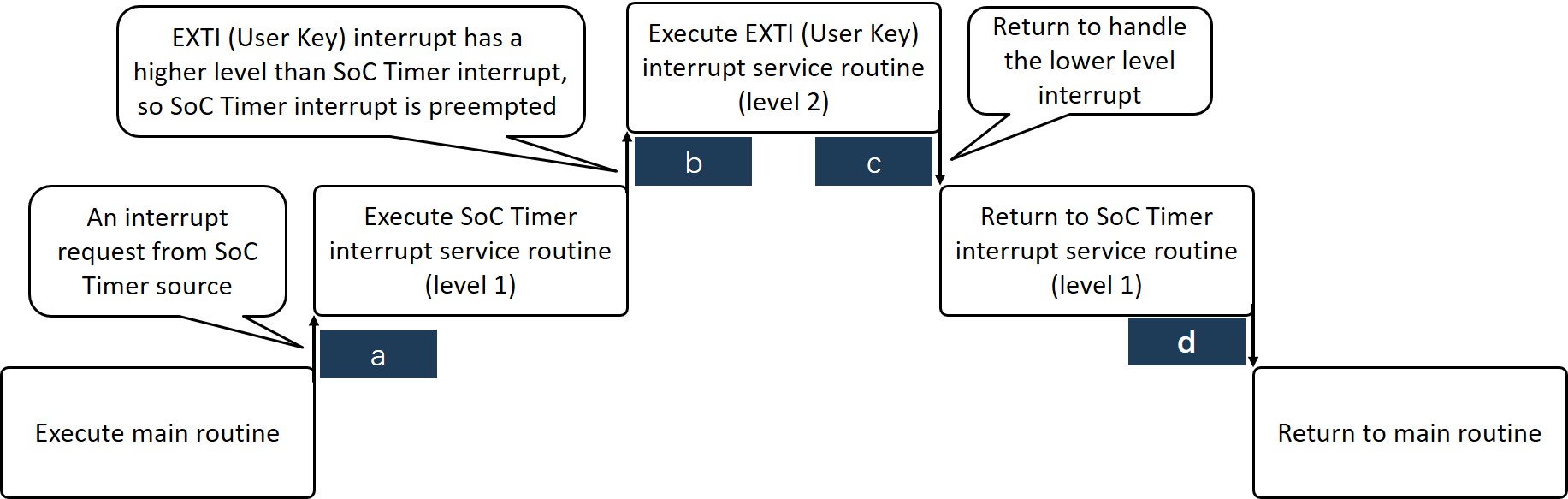

4 1 1 4 Core Feature Nesting Of Interrupts Nuclei Board Labs 0 1 0 The hierarchy of nuclei board labs are shown in the block diagram below. the labs are developed based on the nuclei software development kit (nuclei sdk) which is an open software platform to facilitate the software development of systems based on nuclei processor cores. Core feature: interrupt; 4.then the main stack must have space for 3 exception frames plus however many levels of nested interrupts (i usual only use 1, so no interrupt nesting) plus the stack usage by the handlers (which the compiler will estimate). Interrupt nesting can be achieved between multi level interrupts, but interrupts with different interrupt sources in the same level cannot be nested. it must be processed after one interrupt is processed, and then respond to and process other interrupt sources in the same level. Almost all embedded mcus turn off the cpu global interrupt when the interrupt is pushed, that is, the interrupt nesting is disabled by default. to enable interrupt nesting, the user must interrupt the isr in a peripheral that can be nested. manually turn on the global interrupt of the cpu. While the cpu is doing i o by polling, it is constantly busy and cannot do anything else. in a computer system, i o should be done by interrupts whenever possible. in this chapter, we shall show how to apply the principle of interrupts processing to design and implement interrupt driven device drivers. In multi core microcontroller environments, nesting interrupts become even more complex due to the potential for simultaneous interrupt handling across different cores.

Comments are closed.