12 Implementing 4 Bit Asynchronous Modulo 10 And Synchronous Modulo 10 Counter Using Simulink

4 Bit Asynchronous And Mod 10 Asynchronous Counter Pdf Electronic 12.implementing 4 bit asynchronous modulo 10 and synchronous modulo 10 counter using simulink. Also, the counting sequence may be random for example some cyclic code (8421, 2423 etc). the following method is applied for designing for mod n and any counting sequence.

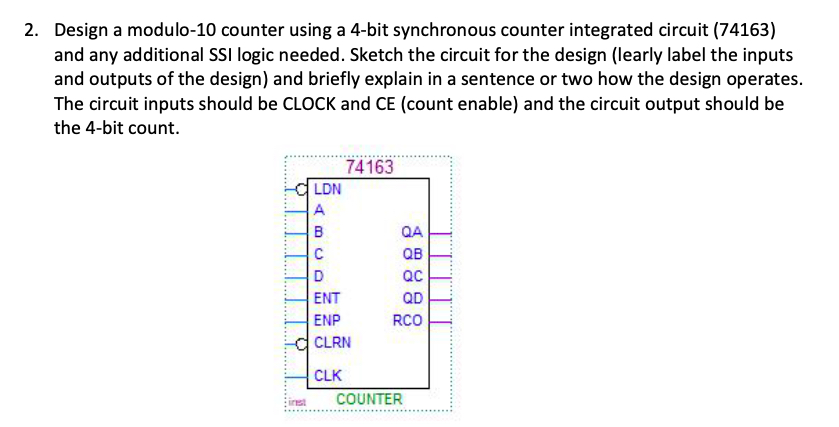

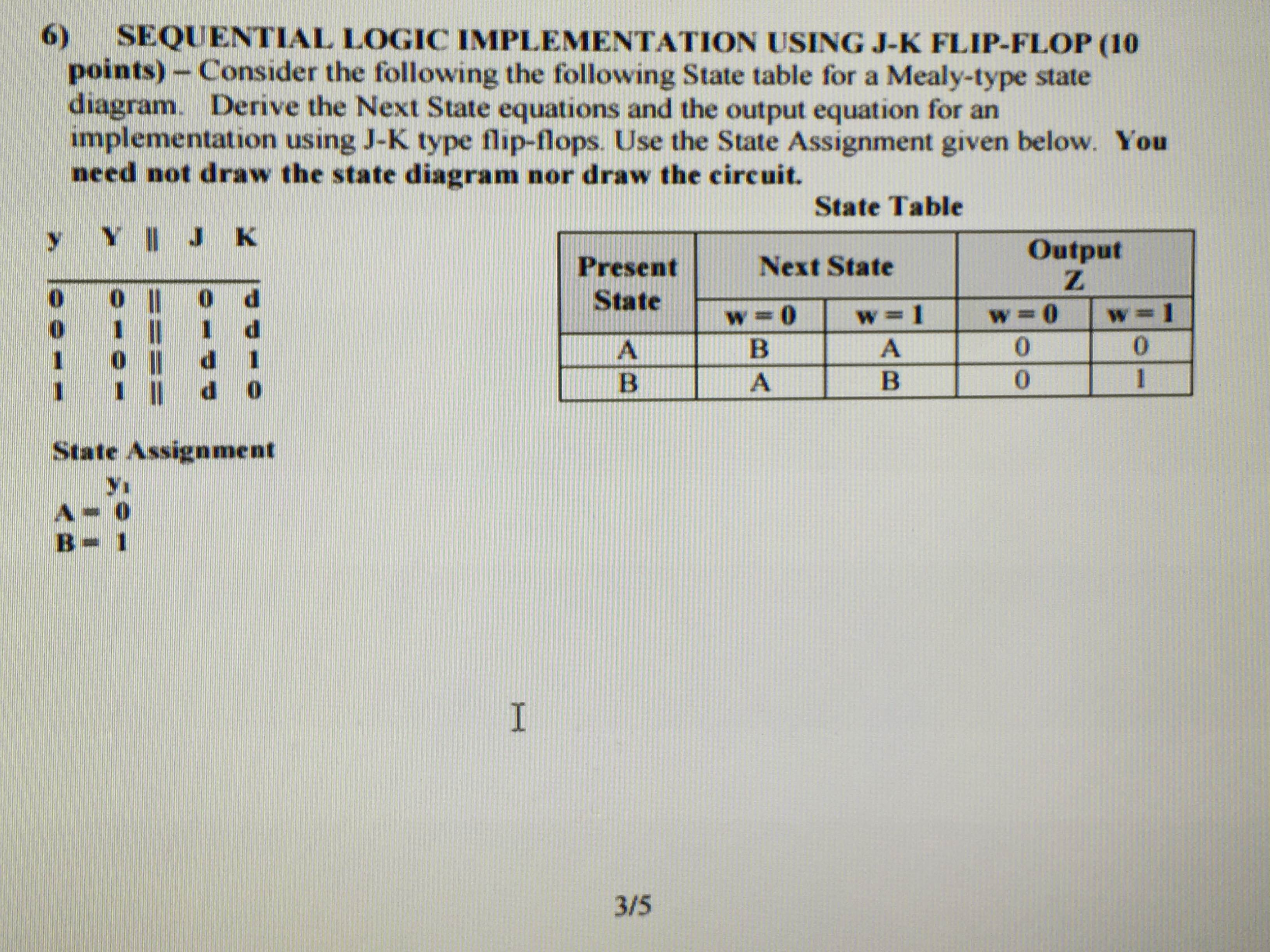

Solved 2 Design A Modulo 10 Counter Using A 4 Bit Chegg This repository contains a pdf report for the project on designing an asynchronous modulo 10 counter. the report includes theoretical background, specifications, state diagrams, transition tables, simplified logic expressions, and simulations. Then, using synchronous or asynchronous combinational logic decoding circuits around a simple counter, we may create whatever kind of mod counter we need by decoding each of the counter’s distinct output states, which allows us to reset the counter to the required count. But why would we want to create an asynchronous truncated counter that is not a mod 4, mod 8, or some other modulus that is equal to the power of two. the answer is that we can by using combinational logic to take advantage of the asynchronous inputs on the flip flop. A 4 bit asynchronous counter is a simple way to count from 0000 to 1111 using flip flops. each flip flop gets its clock from the previous one, creating a ripple effect that causes delays.

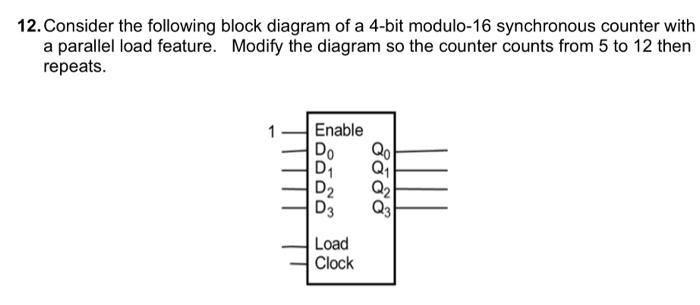

Solved 12 Consider The Following Block Diagram Of A 4 Bit Chegg But why would we want to create an asynchronous truncated counter that is not a mod 4, mod 8, or some other modulus that is equal to the power of two. the answer is that we can by using combinational logic to take advantage of the asynchronous inputs on the flip flop. A 4 bit asynchronous counter is a simple way to count from 0000 to 1111 using flip flops. each flip flop gets its clock from the previous one, creating a ripple effect that causes delays. A 4 bit asynchronous counter and a mod 10 asynchronous counter were implemented successfully using j k flip flops, with the counters' truth tables and outputs observed. Circuit design 4 bits asynchronous counter modulo 10 created by nakrit krechaichana with tinkercad. To design the combinational circuit of valid states, following truth table and k map is drawn: from the above truth table, we draw the k maps and get the expression for the mod 10 asynchronous counter. thus the above k map shows the expression for y which is the reset logic. The one advantage of synchronous counter over asynchronous counter is, it can operate on higher frequency than asynchronous counter as it does not have cumulative delay because of same clock is given to each flip flop.

Solved Counters 4 Bit Modulo 16 Synchronous Chegg A 4 bit asynchronous counter and a mod 10 asynchronous counter were implemented successfully using j k flip flops, with the counters' truth tables and outputs observed. Circuit design 4 bits asynchronous counter modulo 10 created by nakrit krechaichana with tinkercad. To design the combinational circuit of valid states, following truth table and k map is drawn: from the above truth table, we draw the k maps and get the expression for the mod 10 asynchronous counter. thus the above k map shows the expression for y which is the reset logic. The one advantage of synchronous counter over asynchronous counter is, it can operate on higher frequency than asynchronous counter as it does not have cumulative delay because of same clock is given to each flip flop.

Comments are closed.