10 Cache Pdf Cpu Cache Computer Science

Cpu Cache How Caching Works Pdf Cpu Cache Random Access Memory Program access a relatively small portion of the address space at any instant of time. example: 90% of time in 10% of the code. Direct mapped cache: each block has a specific spot in the cache. if it is in the cache, only one place for it. block placement: where does a block go when fetched? block id: how do we find a block in the cache? block replacement: what gets kicked out? now, what if the block size = 2 bytes?.

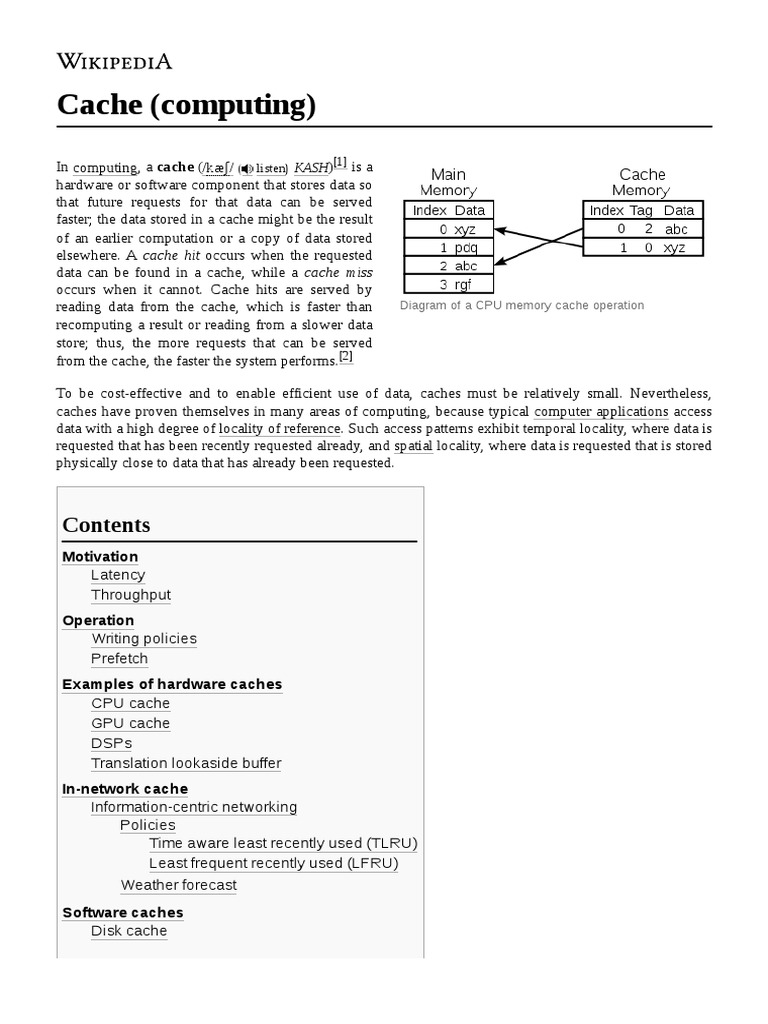

Cache Computing Pdf Cache Computing Cpu Cache Why do we cache? use caches to mask performance bottlenecks by replicating data closer. The “memory wall” processors getting faster more quickly than memory (note: log scale) processor speed improvement: 35% to 55% memory latency improvement: 7%. Multiple levels of “caches” act as interim memory between cpu and main memory (typically dram) processor accesses main memory (transparently) through the cache hierarchy. When virtual addresses are used, the system designer may choose to place the cache between the processor and the mmu or between the mmu and main memory. a logical cache (virtual cache) stores data using virtual addresses. the processor accesses the cache directly, without going through the mmu.

Cache Memory Pdf Cpu Cache Cache Computing Multiple levels of “caches” act as interim memory between cpu and main memory (typically dram) processor accesses main memory (transparently) through the cache hierarchy. When virtual addresses are used, the system designer may choose to place the cache between the processor and the mmu or between the mmu and main memory. a logical cache (virtual cache) stores data using virtual addresses. the processor accesses the cache directly, without going through the mmu. In computer architecture, almost everything is a cache! branch target bufer a cache on branch targets. most processors today have three levels of caches. one major design constraint for caches is their physical sizes on cpu die. limited by their sizes, we cannot have too many caches. Idea: cache coherence aims at making the caches of a shared memory system as functionally invisible as the caches of a single core system. Pdf | on oct 10, 2020, zeyad ayman and others published cache memory | find, read and cite all the research you need on researchgate. Cmu school of computer science.

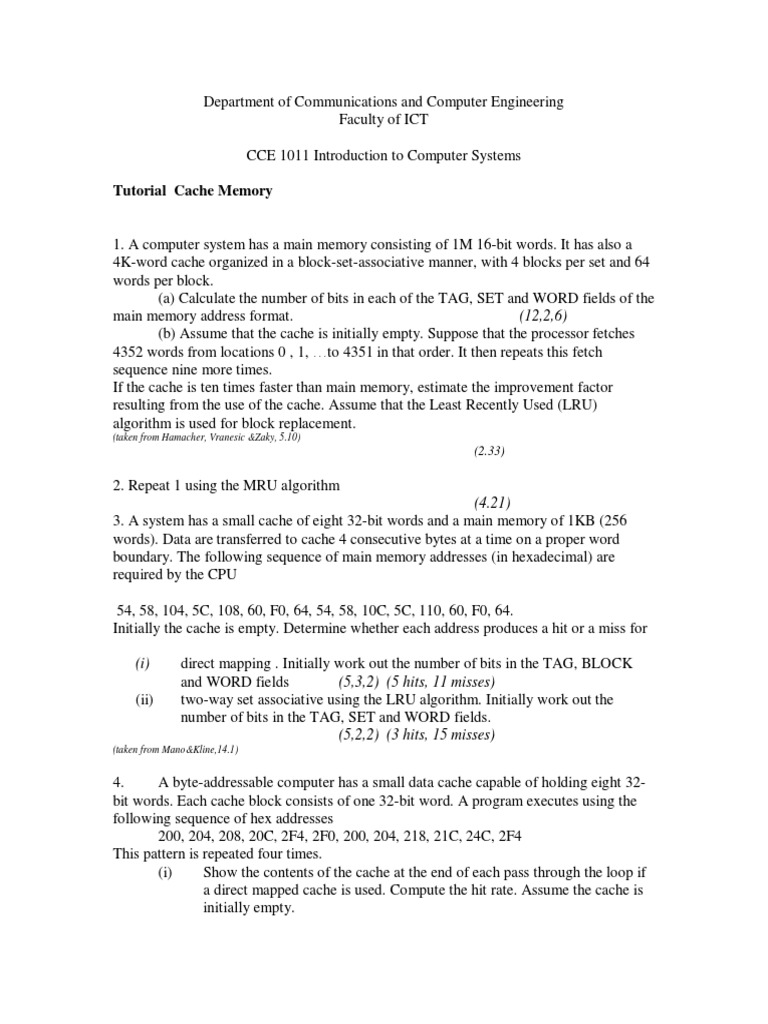

Cce1011 Tut Cache Pdf Cpu Cache Computer Science In computer architecture, almost everything is a cache! branch target bufer a cache on branch targets. most processors today have three levels of caches. one major design constraint for caches is their physical sizes on cpu die. limited by their sizes, we cannot have too many caches. Idea: cache coherence aims at making the caches of a shared memory system as functionally invisible as the caches of a single core system. Pdf | on oct 10, 2020, zeyad ayman and others published cache memory | find, read and cite all the research you need on researchgate. Cmu school of computer science.

Virtual And Cache Memory Implications For Enhanced Pdf Cpu Cache Pdf | on oct 10, 2020, zeyad ayman and others published cache memory | find, read and cite all the research you need on researchgate. Cmu school of computer science.

Comments are closed.